Method for manufacturing layers required by integrated circuit layout registration

A technology of integrated circuits and manufacturing methods, which is applied in the fields of electrical digital data processing, special data processing applications, instruments, etc., and can solve problems such as the inability to guarantee the accuracy of graphic splicing, the inability to process image splicing, and the inability to complete graphics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

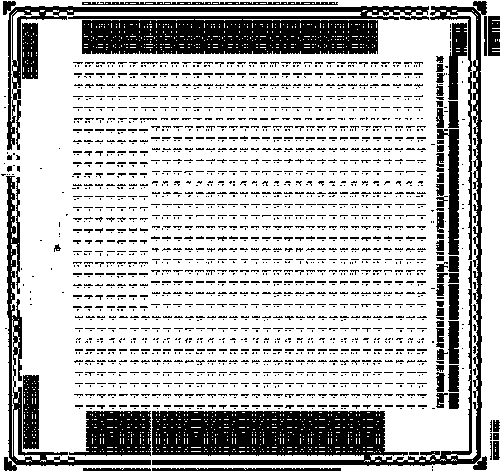

[0019] Taking the layout of a certain chip as an example, the chip adopts 0.35μm2P3M process, 15 layers, and the chip area is 6.83mm×6.43mm.

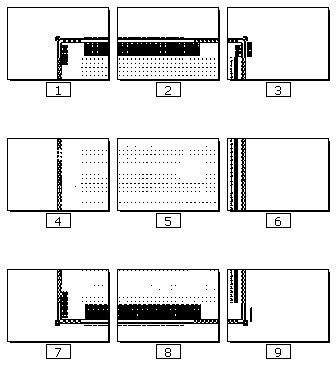

[0020] 1. Layout level flattening: According to the gds format data file of the chip layout, import the file, open the general diagram of the chip layout, and select the flattening command to flatten the units of its hierarchical design. The flattened general diagram contains 15 layers of graphics from L1 to L15;

[0021] 2. Printing settings: Select a certain layer with technological characteristics such as contact hole layer L8, set appropriate printing parameters according to the size of the chip layout, such as printing ratio, number of printed sheet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com