A kind of manufacturing method of coreless thin substrate

A manufacturing method and technology for thin substrates, which are applied in the directions of multilayer circuit manufacturing, semiconductor/solid-state device manufacturing, and electrical connection formation of printed components, etc., can solve the problems of increasing the difficulty of circuit thickness control, difficulty in arbitrarily interconnecting circuits, etc., and achieve low cost. , the effect of reducing thickness and reducing process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] The manufacturing method of the coreless thin substrate of this embodiment includes the following steps:

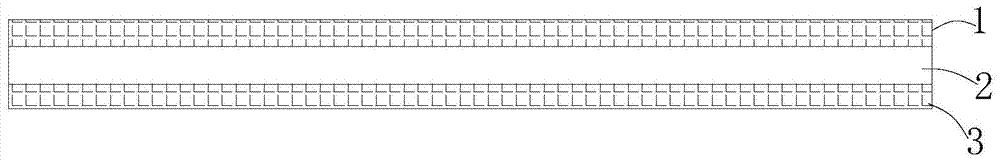

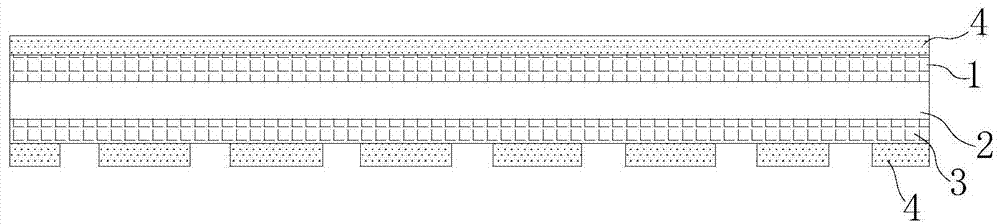

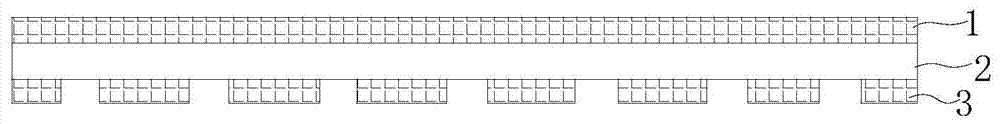

[0043] a. The first copper foil 1, the first prepreg 2, and the second copper foil 3 are stacked sequentially from top to bottom for the first pressing, the first pressing is low-temperature vacuum pressing, and the pressing temperature is the first prepreg The temperature at which the viscosity of 2 is the lowest is preferably 110°C in this embodiment, and is pressed with a vacuum laminating machine under a certain pressure for 15 to 25 minutes, preferably 20 minutes in this embodiment, to obtain the first substrate, such as figure 1 As shown, that is, a double-sided copper-clad prepreg; the first substrate is subjected to dry film pretreatment, such as cleaning or acid treatment, and then the first dry film 4 is pressed on the surface of the first copper foil 1 and the second copper foil 3 respectively, and the The first dry film 4 pressed on the surface of the s...

Embodiment 2

[0050] The difference between this embodiment and Embodiment 1 is that after step d, step e2 replaces step e1, and the third prepreg 14 is respectively pressed on both sides of the substrate model prepared in step d, and the third prepreg 14 is formed by lamination. Multilayer circuits 15 with a specific number of layers are stacked on top to prepare multilayer odd-numbered laminates, such as Figure 15 As shown, the multi-layer circuit is also connected to the first circuit and the third circuit respectively through blind holes. The build-up method used in this embodiment is just a conventional method for making a multi-layer board, and will not be repeated here.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com