50% duty ratio clock generation circuit

A clock generation circuit and duty cycle technology, applied in the direction of generating electrical pulses, pulse generation, electrical components, etc., can solve the problems of the output phase being unable to be locked, the periodic error of the output clock signal duty cycle, and the phase jitter, etc. Small design difficulty and power consumption, the effect of improving the signal-to-noise ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043]In order to make the technical problems, technical solutions and advantages to be solved by the present invention clearer, the following will describe in detail with reference to the drawings and specific embodiments.

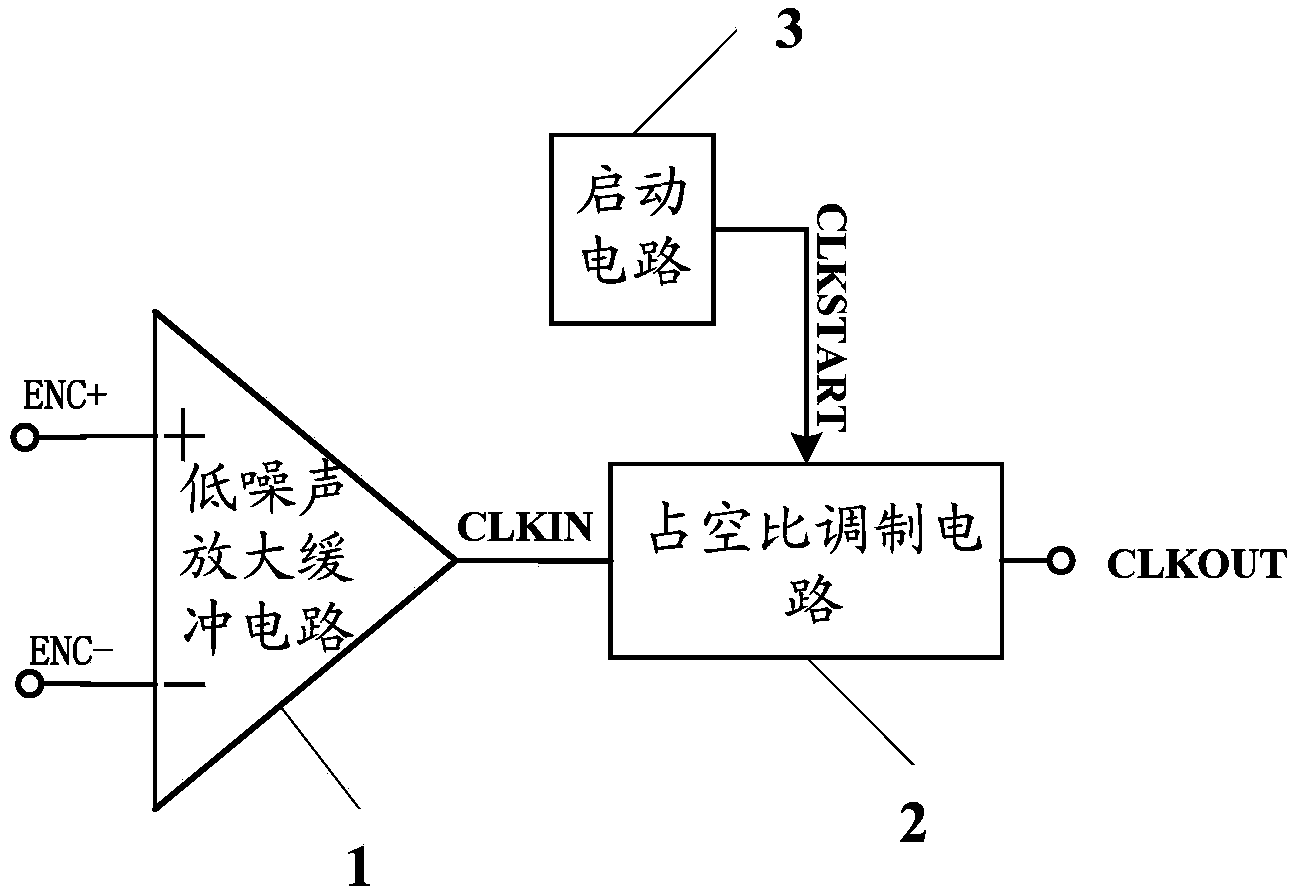

[0044] The present invention aims at the problem that the two-phase non-overlapping clocks of the quantizer in the analog-to-digital conversion circuit do not have the same pulse width, and the working speed of the quantizer is low, and provides a 50% duty ratio clock The generating circuit converts the differential clock signal into a single-ended clock signal through a low-noise amplification buffer circuit, and modulates the duty ratio of the single-ended clock signal to generate a clock signal with a duty ratio of 50%, which reduces the The design difficulty and power consumption of the sample-and-hold circuit in the digital conversion circuit improve the signal-to-noise ratio (SNR) and clutter-free dynamic range (SFDR) of the analog-to-digital convers...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com