Parallel multi-core FPGA digital image real-time zooming processing method and device

A digital image and processing method technology, which is applied in the field of parallel multi-core FPGA digital image real-time scaling processing and devices, can solve the problem of high system cost, and achieve the effect of taking into account processing efficiency, reducing calculation clock frequency, and reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0043] With the development of technology, the demand for video display technology is no longer solely limited to how to display higher-resolution video information on a larger screen, but also how to enlarge low-resolution video information to the corresponding display in real time. The screen size is displayed on the high resolution screen. It is not difficult to see from this that the development of video display technology is no longer limited only by the display technology itself, but in some applications is more limited by the quality, real-time, processing method and processing chip operation of the required video information. ability.

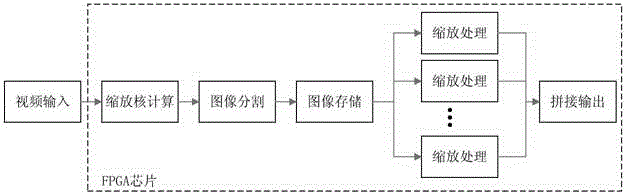

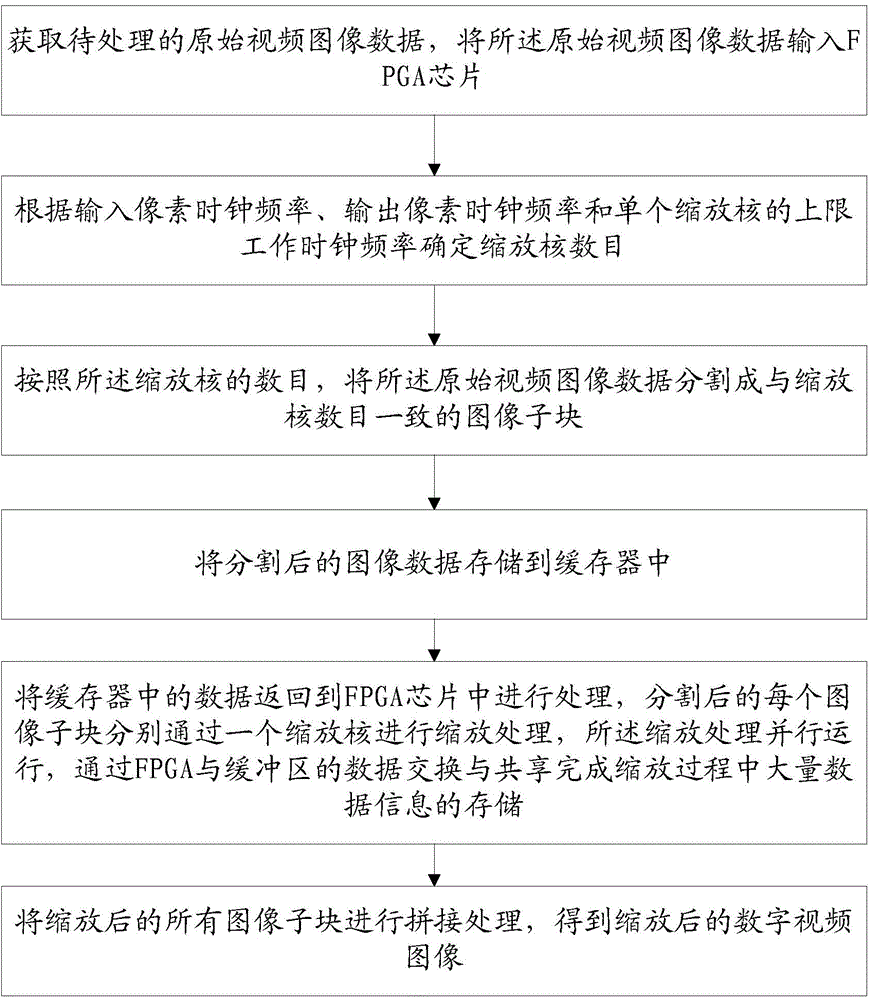

[0044] Based on this, this embodiment provides a high-efficiency parallel digital video image real-time scaling processing method to balance the contradiction between the system processing capacity and the higher requirements for throughput and real-time performance of digital video image scaling, thereby reducing System cost and the purp...

Embodiment 2

[0062] In this embodiment, when selecting the required number of scaling cores, select the smallest number of scaling cores, and input the pixel clock frequency CLK in , Output pixel clock frequency CLK out , After comparing, get the highest frequency of the pixel clock CLK=max{CLK in , CLK out }, the upper limit working clock frequency of a single scaling core is CLK Smax , Then the number of scaling cores n is a positive integer, then when CLK / CLK Smax When it is an integer, n=CLK / CLK Smax ; When CLK / CLK Smax When it is a non-integer, n=[CLK / CLK Smax ]+1, [·] means rounding operation.

[0063] In addition, in this embodiment, the method of longitudinal uniform division is adopted when dividing the original video image data. Since the monitor works in a raster scan (raster scan) mode, the pixels are output in order from the top left to the bottom right. In this embodiment, the video image is uniformly divided longitudinally according to the characteristics of the raster sc...

Embodiment 3

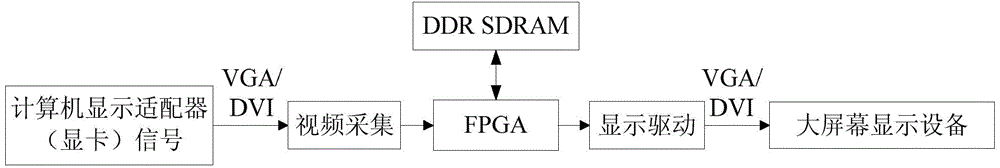

[0066] A device using the parallel multi-core FPGA digital image real-time scaling processing method described in embodiment 1 or 2, comprising

[0067] Input module: Use the SiI1161 chip of Silicon Image to obtain the original video image data to be processed, and input the original video image data into the Spartan-6XC6SLX100 FPGA chip produced by Xilinx;

[0068] Scaling core calculation module: Determine the number of scaling cores according to the input pixel clock frequency, output pixel clock frequency and the upper limit working clock frequency of a single scaling core;

[0069] Segmentation module: segment the original video image data according to the number of zoom cores and obtain each segmented image sub-block;

[0070] Storage module: Store the divided image data in the external DDR buffer, the model is Micron MT47H32M16-25;

[0071] Scaling module: Return the data in the buffer to the FPGA chip for processing. Each image sub-block after segmentation undergoes a scaling co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com