PID-resistant solar cell manufacturing method

The invention relates to a technology for solar cells and a manufacturing method, which can be applied to circuits, photovoltaic power generation, electrical components, etc., and can solve the problems of reducing the anti-reflection effect of silicon nitride and silicon oxide composite films, reducing the utilization rate of solar cells, and affecting the efficiency of solar cells. , to achieve good surface passivation effect, improve photoelectric conversion efficiency, excellent anti-PID effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

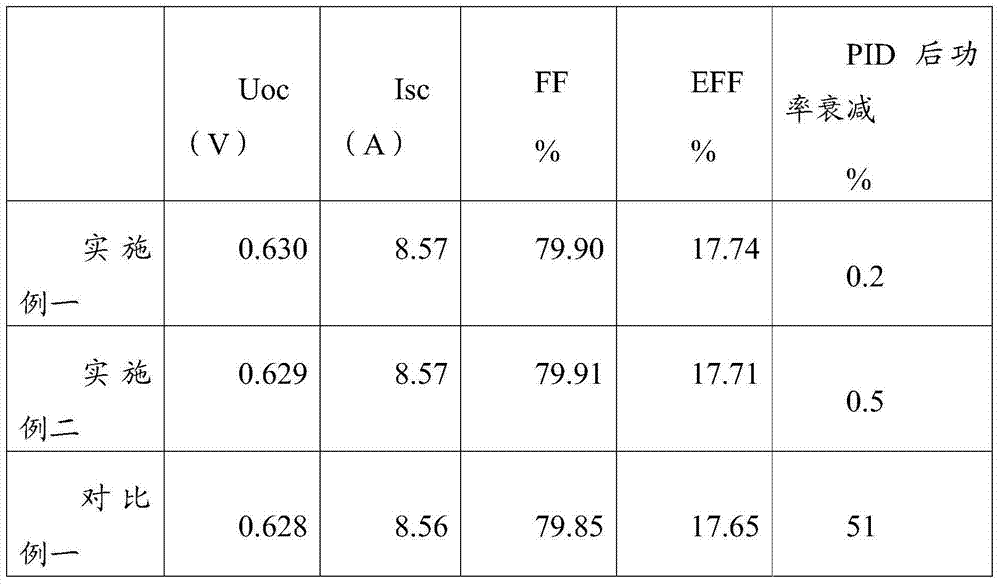

Examples

Embodiment 1

[0055] A method for preparing an anti-PID film by using ultraviolet excited ozone oxidation, the steps of which include:

[0056] (1) The diffused silicon wafer is etched to remove the edge, and the phosphosilicate glass layer is cleaned and removed;

[0057] Among them, HF was used for cleaning, the volume concentration of HF solution was 4%, the solution temperature was 20°C, and the cleaning time was 200s;

[0058] (2) After 15 minutes, the diffusion surface of the silicon wafer is irradiated with ultraviolet rays with a wavelength of 172nm and a light intensity of 100W / m2, and compressed air with a flow rate of 10sccm is passed around the silicon wafer, and the temperature of the silicon wafer is 20℃. The distance between the surface of the wafer is 0.5cm, the processing time is 5s, the residual organic matter on the surface of the silicon wafer is removed, and the oxide film is grown to a thickness of 0.6nm;

[0059] (3) After 10min, the silicon nitride film is deposited...

Embodiment 2

[0062] A method for preparing an anti-PID film using ultraviolet light, the steps comprising:

[0063] (1) The diffused silicon wafer is etched to remove the edge, and the phosphosilicate glass layer is cleaned and removed;

[0064] Among them, HF was used for cleaning, the volume concentration of HF solution was 5%, the solution temperature was 21°C, and the cleaning time was 55s;

[0065] (2) After 5s, use ultraviolet rays with a wavelength of 185nm and a light intensity of 200W / m2 to irradiate the diffusion surface of the silicon wafer. The compressed air with a flow rate of 8sccm is passed around the silicon wafer, and the temperature of the silicon wafer is 22°C. The ultraviolet rays pass through the compressed air and reach the silicon wafer. The distance from the surface of the wafer is 0.8cm, the processing time is 8s, the residual organic matter on the surface of the silicon wafer is removed, and the oxide film is grown to a thickness of 0.8nm

[0066] (3) after 15mi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Light intensity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com