Thin film transistor and manufacturing method thereof, array substrate and display device

A technology for thin film transistors and a manufacturing method, applied in the field of liquid crystal display, can solve the problems of poor film stability and reduced film deposition rate, and achieve the effects of reducing hydrogen content, fully decomposing silane, and avoiding metal oxide reactions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

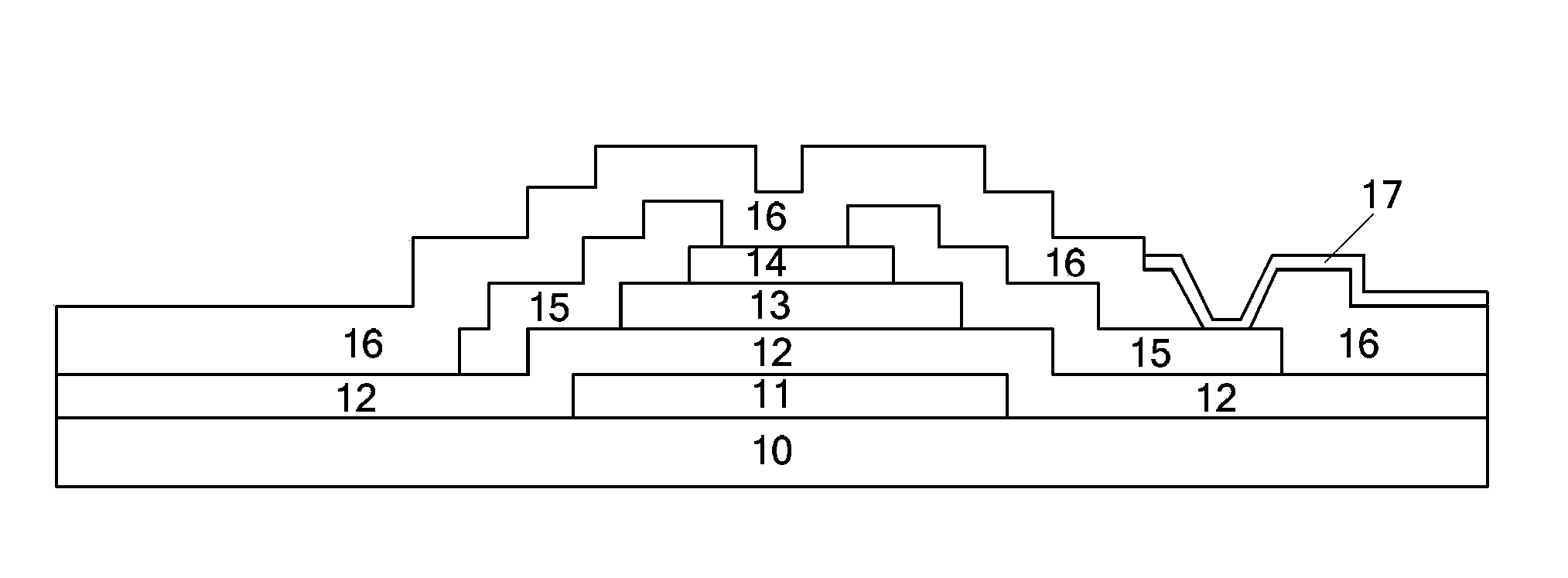

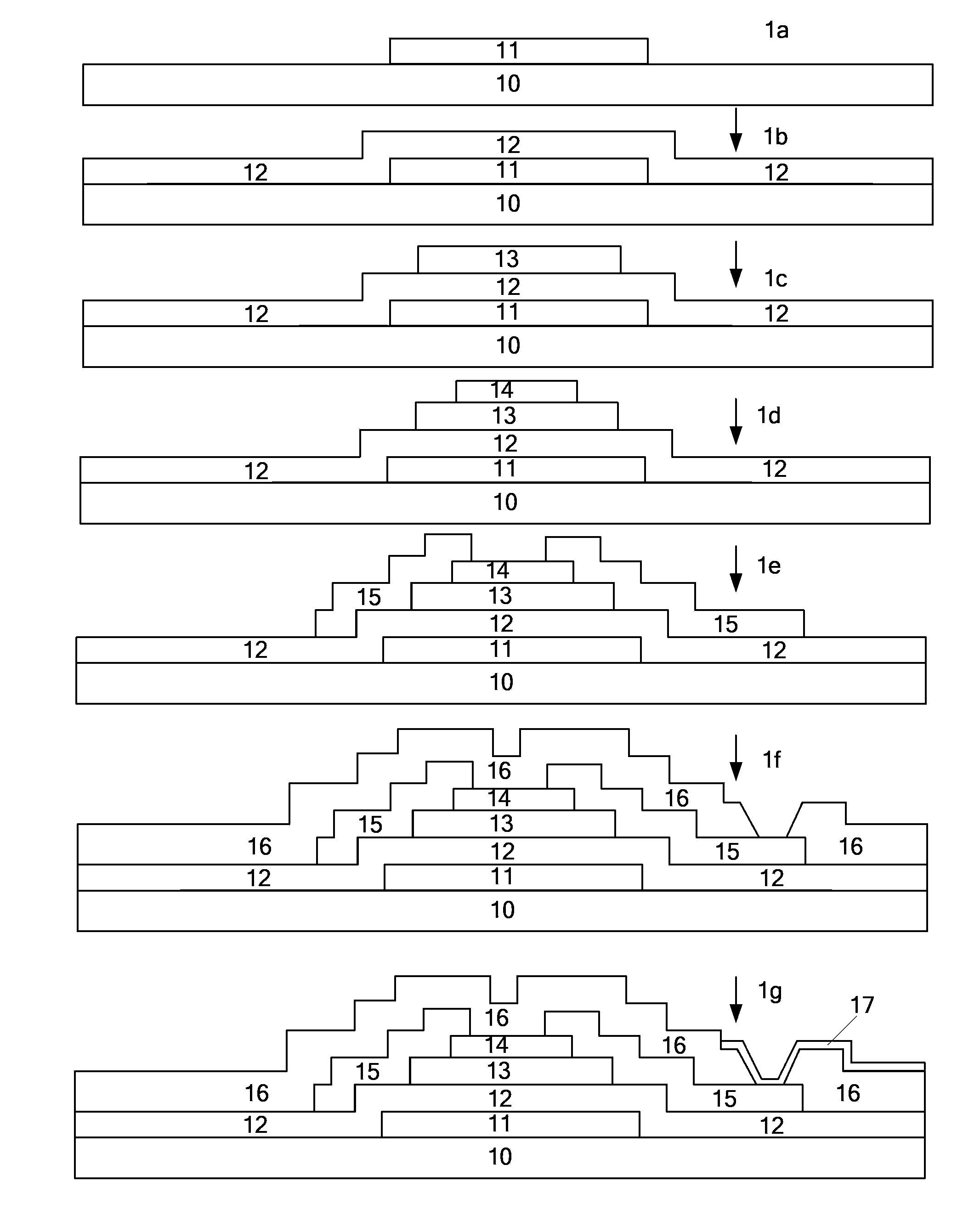

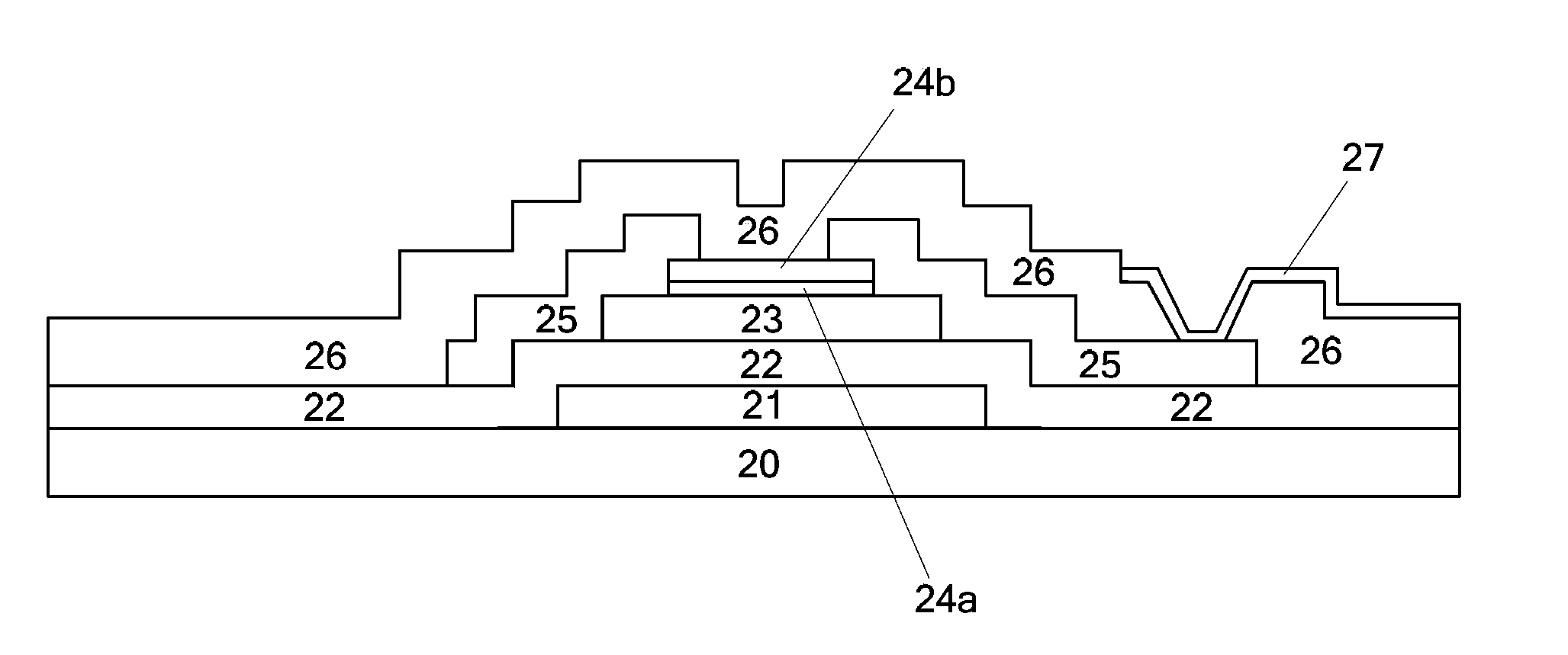

[0055] The basic idea of the present invention is: at least one insulating layer of the thin film transistor is manufactured by a double-layer structure process, that is, the bottom insulating layer and the upper insulating layer are manufactured separately, so that the bottom layer can be made by using different process conditions according to the properties of the insulating layer film. The insulating layer and the upper insulating layer, and the lower insulating layer is used as a barrier layer to make the upper insulating layer, so that the upper insulating layer can be made under the conditions of higher temperature and gas flow than the lower insulating layer, and the characteristics of the insulating layer film are improved. and film deposition rate.

[0056] Taking the etch stop layer in an oxide thin film transistor as an example, the thin film transistor and its manufacturing method of the present invention will be described in detail in combination with specific em...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com