How to form a CMOS transistor

A technology of transistors and semiconductors, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as the complexity of fin CMOS transistor technology, and achieve the effects of saving photolithography steps, easy removal, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

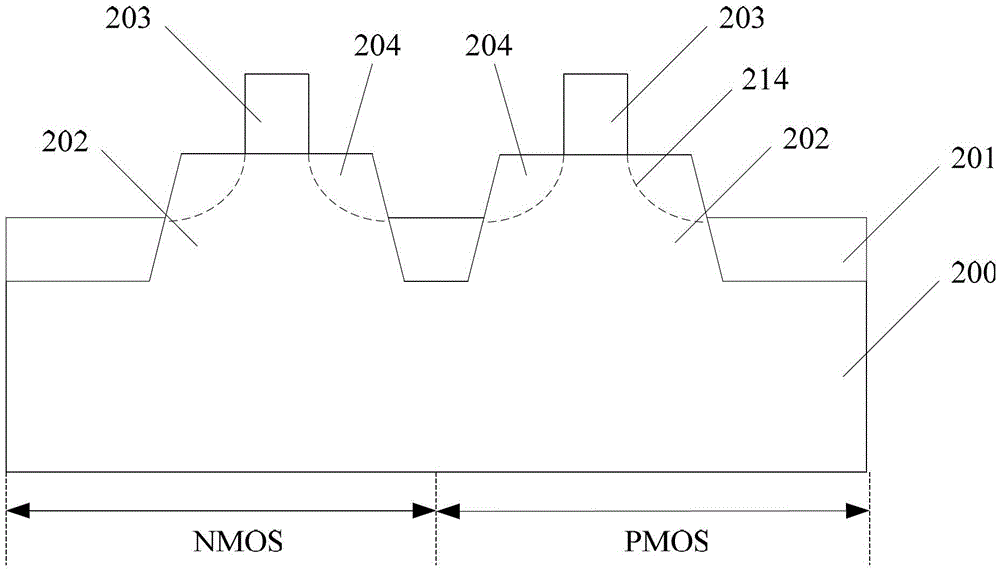

[0033] It can be seen from the background art that in the prior art, in the process of forming a fin-type CMOS transistor with stress, in order to form the source and drain regions of NMOS and PMOS respectively, and to introduce stress in the channel region of NMOS and PMOS, it is necessary to use multiple The photolithography process is complex and costly.

[0034] The inventors of the present invention have studied the process of forming fin-type CMOS transistors in the prior art, and found that when doping the source and drain regions of NMOS in the prior art, it is necessary to form a mask layer covering the PMOS area by photolithography, and carry out N-type ion Implantation: When doping the source and drain regions of PMOS, photolithography is required to form a mask layer covering NMOS for P-type ion implantation. However, in order to introduce stress into the channel regions of the NMOS and PMOS transistors later, it is necessary to remove the source and drain regions ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com