1-D/2-D hybrid architecture FFT (Fast Fourier Transform) processor

A hybrid architecture and processor technology, applied in complex mathematical operations and other directions, can solve the problems of large data storage resources and slow operation speed, and achieve the effect of less storage resources, improved speed, and high operation speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

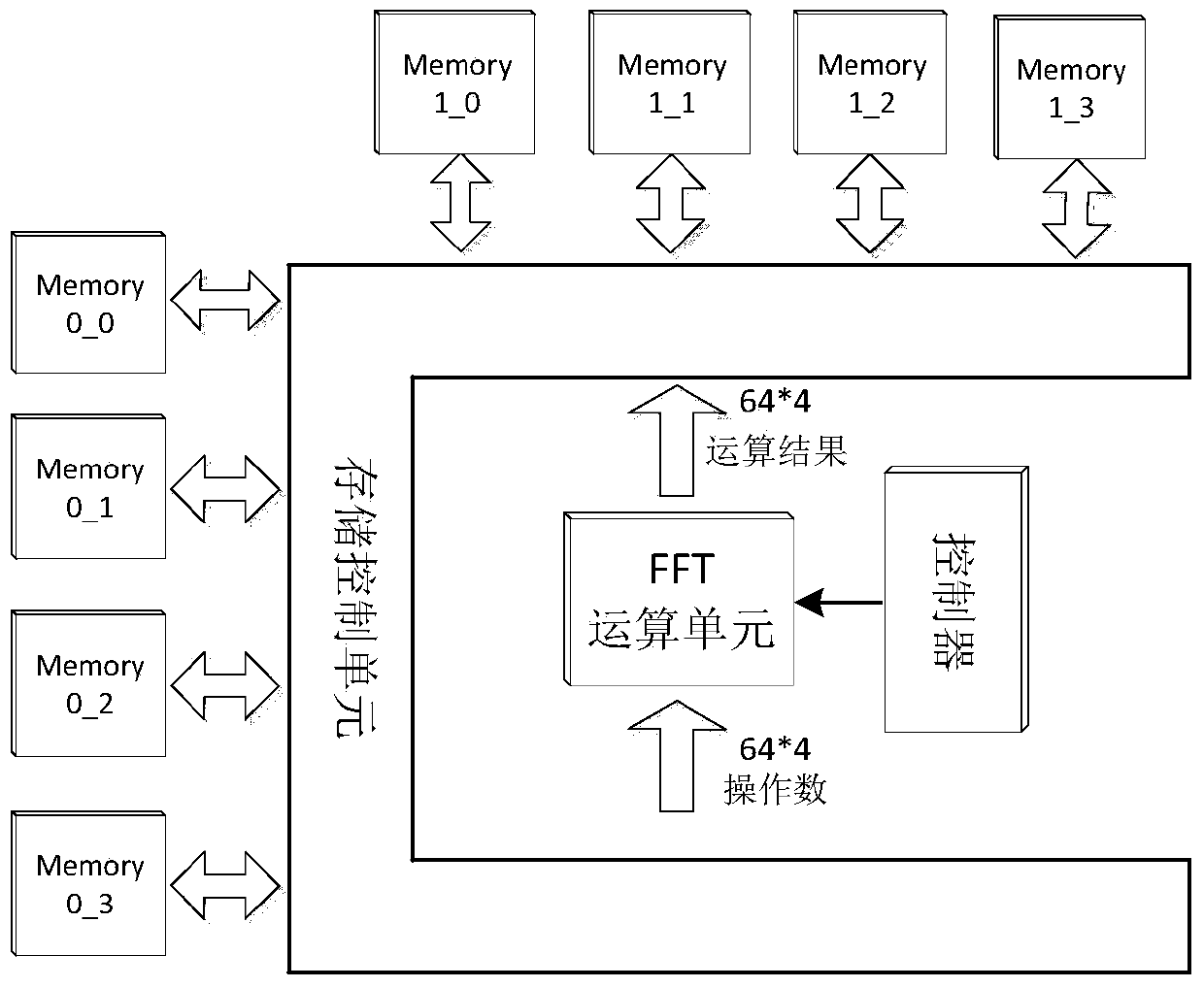

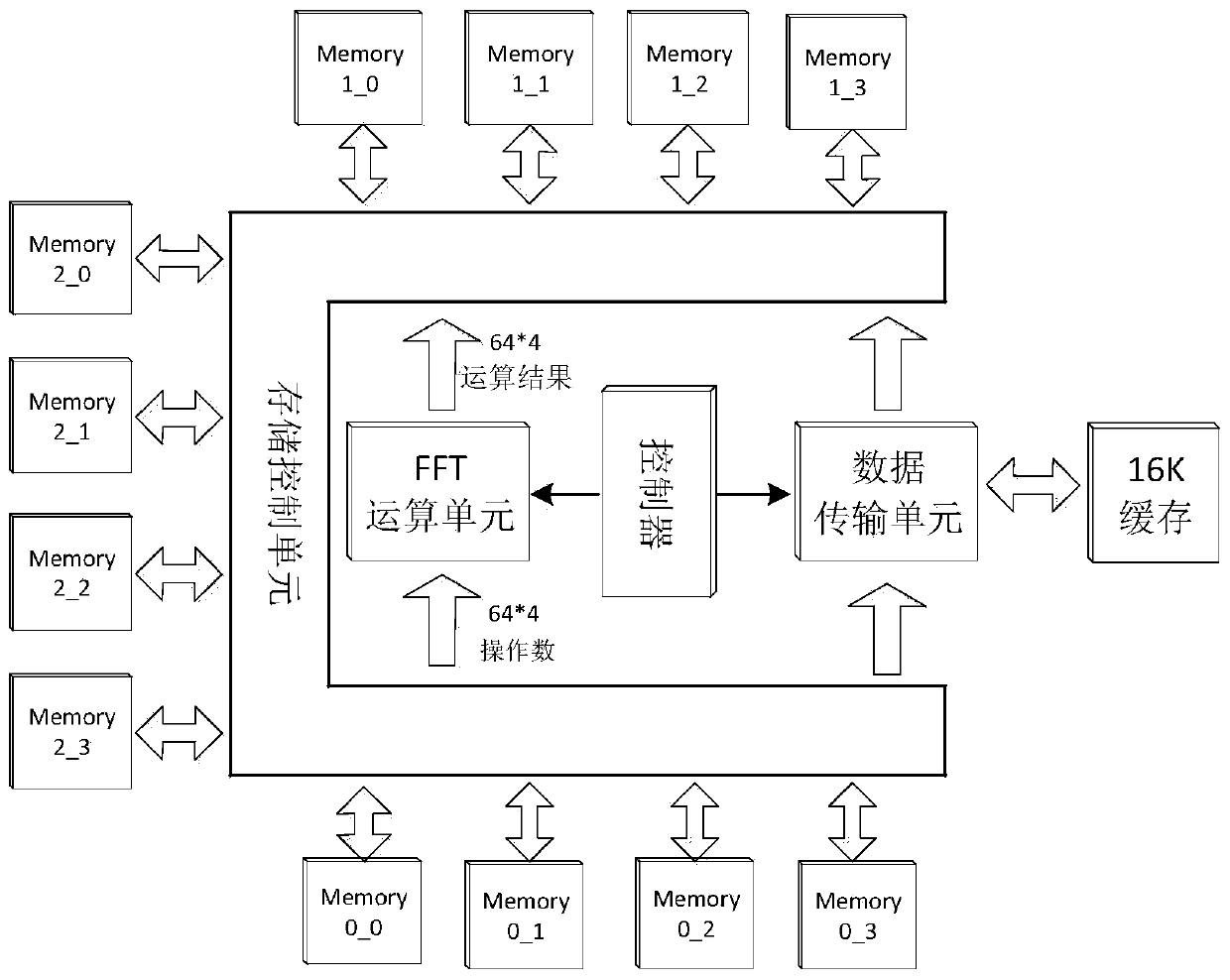

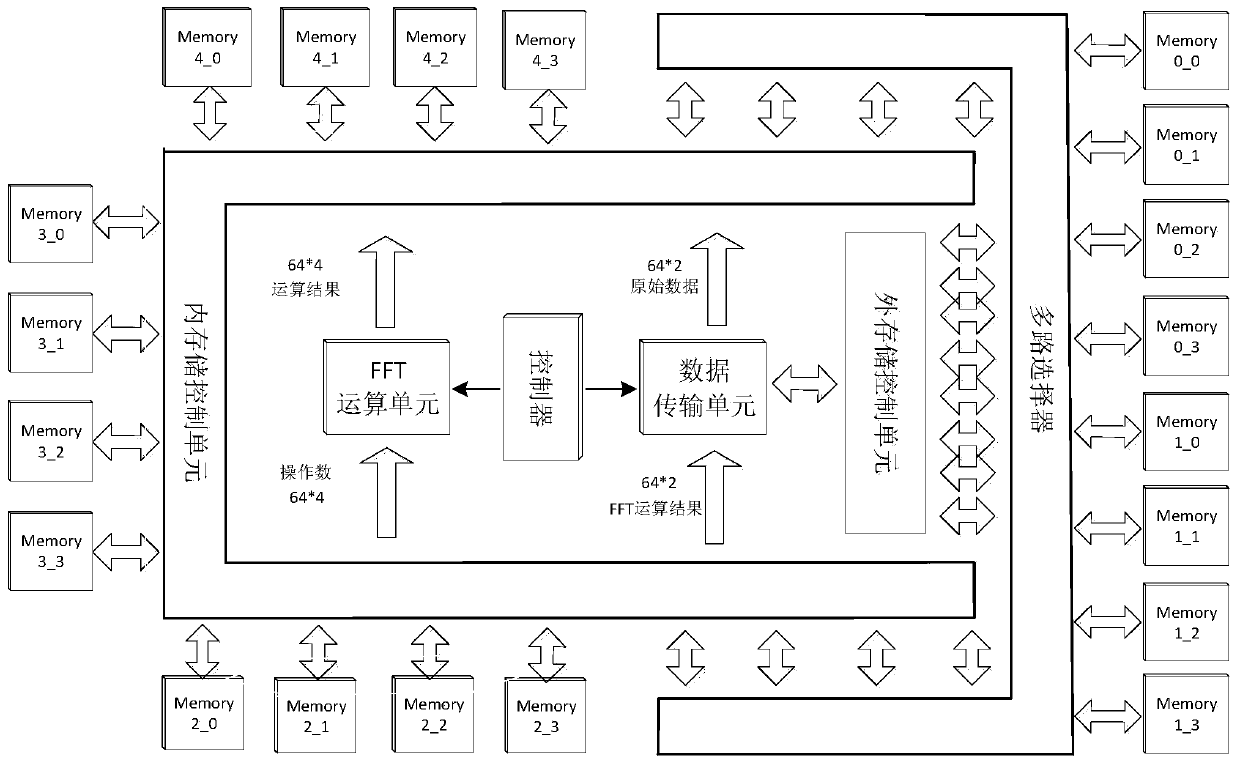

[0049] Such as image 3 As shown, the 1-D / 2-D hybrid architecture FFT processor in this embodiment includes a controller, a storage system, a data exchange network, a data transmission unit and an FFT calculation unit;

[0050] The controller is used to control the data transmission unit and the FFT operation unit;

[0051] The storage system includes 2 groups of 4*2K on-chip data memory (Memory0 / 1_x) and 3 groups of 4*32 temporary storage (Memory2 / 3 / 4_x), 2 groups of 4*2K on-chip data memory and 3 groups of 4*32 temporary storage Adopt simple dual-port RAM; according to 16K=128*128, the maximum one-dimensional FFT that needs to be processed in two-dimensional FFT processing mode is 128 points. In order to save storage resources, the FFT processor uses three groups of 4*32 temporary memory ping-pong operations to complete the ranks One-dimensional FFT operation.

[0052] The data exchange network includes an internal storage control unit, an external storage control unit and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com