BICMOS circuit converting ECL logic level into MOS logic level

A MOS logic, logic level technology, applied in the direction of logic circuit connection/interface arrangement, logic circuit coupling/interface using field effect transistors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

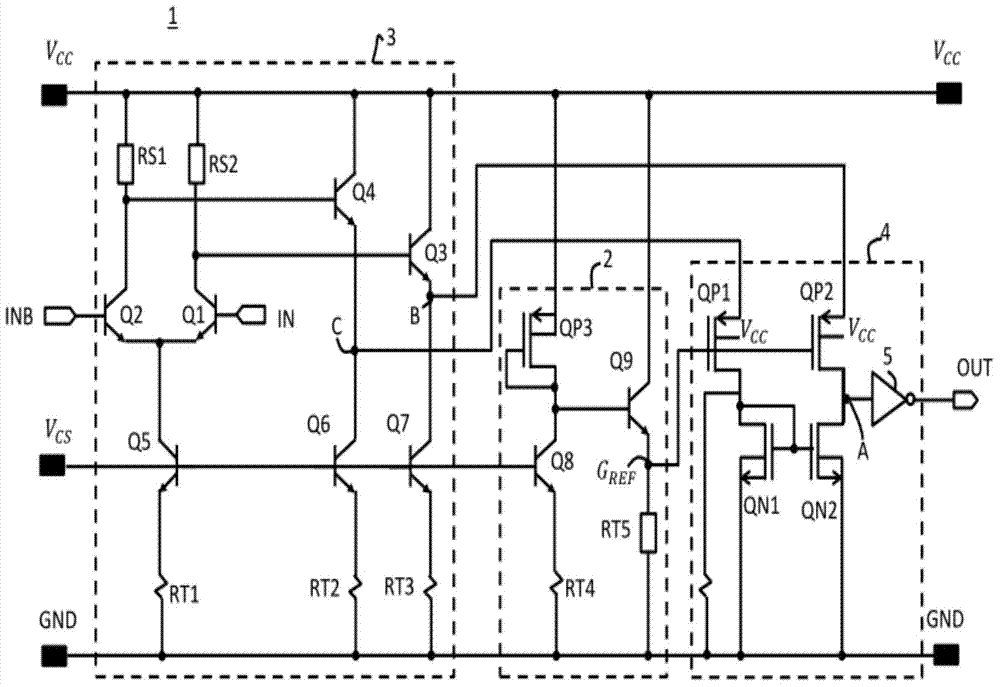

[0023] The device of the present invention, ECL to CMOS converter 1, in figure 2 is illustrated, including the reference voltage stage 2, used to develop an independent voltage reference source for the ECL to CMOS converter. It should be understood that the converter circuits described here can also be used in phase locked loop circuits, clock recovery circuits, or other circuit designs requiring fast converters. about figure 2 , an ECL input stage 3 of the ECL to CMOS converter 1, comprising a first input transistor Q1 and a second input transistor Q2, the first input transistor Q1 receives the first input signal IN on its control node, the second input transistor Q2 receives at its control node a second input signal INB which complements the first input signal IN. Preferably, Q1 and Q2 are connected to the high potential supply rail V CC .

[0024] The bipolar ECL input stage 3 further includes a first emitter follower transistor Q3 and a second emitter follower Q4, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com