Multi-channel sinusoidal signal generator and method for generating multi-channel sinusoidal signals

A sinusoidal signal, multi-channel technology, applied in electrical components and other directions, can solve the problems of jitter, low frequency of sinusoidal signals, affecting waveform quality, etc., to achieve the effect of low device cost, easy channel number, and low hardware cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

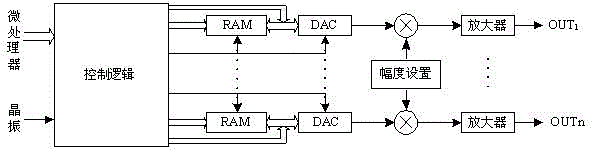

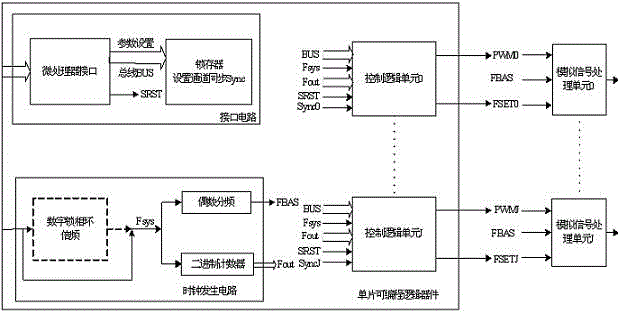

[0039] to combine image 3 , The 56-channel sinusoidal signal generating circuit of the present invention is composed of a single-chip FPGA device EP2C8Q208 and 56 completely identical analog signal conversion units. figure 2 The FPGA in it has built-in interface circuit, clock system generating circuit, and 56 control logic units with the same structure. The frequency of the external crystal oscillator is 40MHz, and the frequency multiplied by the digital phase-locked loop is 280MHz system clock Fsys. Driver requirements. Its working principle has been discussed in detail in the summary of the invention.

[0040] Figure 4 for image 3 The functional block diagram of the control logic unit in , and its working principle has been discussed in detail in the summary of the invention. Each control logic unit generates the amplitude control signal PWM and the phase frequency control signal FSET. The microprocessor sets the 16Bit amplitude word, 40Bit frequency word, and 12Bi...

Embodiment 2

[0043] to combine Figure 6 , The 120-channel sinusoidal signal generating circuit of the present invention is composed of a single-chip FPGA device EP2C20F484 and 120 identical analog signal conversion units. Figure 5 The FPGA in it has built-in interface circuit, clock system generation circuit, and 120 control logic units with the same structure. After FBAS buffers, it outputs through multiple pins of FPGA to meet the driving requirements of 120 channels. The functional indicators of each control logic unit and analog conversion unit are consistent with those of the first embodiment.

Embodiment 3

[0045] to combine Figure 7 , The 10-channel sinusoidal signal generating circuit of the present invention is composed of a single-chip CPLD device EPM1270T144 and 10 identical analog signal conversion units.

[0046] Figure 7 The CPLD has built-in interface circuit, clock generation circuit, and 10 control logic units with the same structure. 50MHz external crystal oscillator frequency direct system clock Fsys, without using digital phase-locked loop; Fsys is the fundamental frequency square wave FBAS after 2048 frequency division. Each control logic unit generates an amplitude control signal PWM and a phase frequency control signal FSET. The microprocessor sets the parameters of each channel as follows: 16Bit amplitude word, 36Bit frequency word, 12Bit phase word, the normal operating frequency of the phase frequency control signal FSET is variable within the range of 20kHz based on the FBAS frequency, and the sinusoidal signal frequency band generated by each channel is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com