SRAM type FPGA single event upset effect simulation method

A single-event flipping and simulation method technology, applied in the field of SRAM-type FPGA single-event flipping effect simulation, can solve the problems of limited irradiation source conditions, limited ground irradiation test accelerators for aerospace components, etc. Precise results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

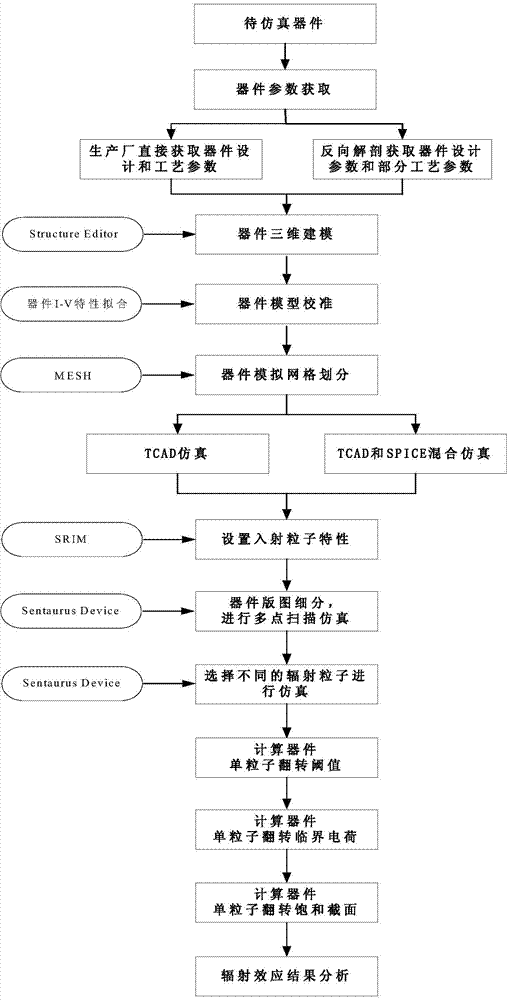

[0062] Step 1: Obtain the design and process parameters of the device to be simulated.

[0063] Enter the detailed process flow and related process parameters and device structure parameters, use the lyt layout information provided by the process manufacturer, and perform process simulation through Sprocess software to obtain device doping information and establish a three-dimensional model of the device; or use the GDS provided by the design unit Layout file, through ICworkbench EV plus software to realize the conversion of GDS file, and obtain the design and process parameters of the simulated device.

[0064] Step 2: Use modeling tools to construct the three-dimensional geometry of the device, and set the doping area, concentration and discretization strategy of the device.

[0065] Step 2.1: Select corresponding process materials for different regions of the device;

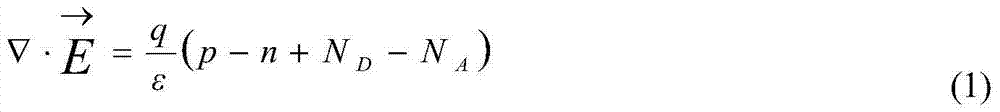

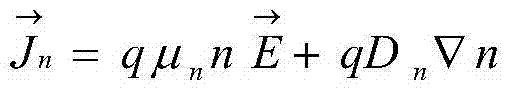

[0066] Step 2.2: Design and set process parameters according to the process structure of the transistor. ...

Embodiment 2

[0082] If the unit circuit structure of the simulation device is less than six transistors, the method also needs to go through the specific selection of the following steps in addition to steps 1-4 and steps 6-9 in Embodiment 1:

[0083] Step 1: Use the device-level TCAD simulation method to perform single event effect simulation.

[0084]The device-level three-dimensional model is established one by one for the transistors inside the simulated device. When setting the initial heavy ion incidence, the drain of the TCAD model is connected to a positive potential, the gate is connected to 0, and the source is grounded. Particles with different linear energy transmission values are incident on the sensitive area of the transistor (NMOS drain), and the sensitive node is detected to determine whether a single event flip occurs.

[0085] Taking a certain 300,000-gate SRAM FPGA as an example, the device single-event flip LET threshold obtained by using the method of the present...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com