Method for manufacturing through substrate via (tsv), tsv structure of through silicon via and control method of tsv capacitance

A manufacturing method and substrate technology, which are used in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., to improve signal interference problems and avoid attenuation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

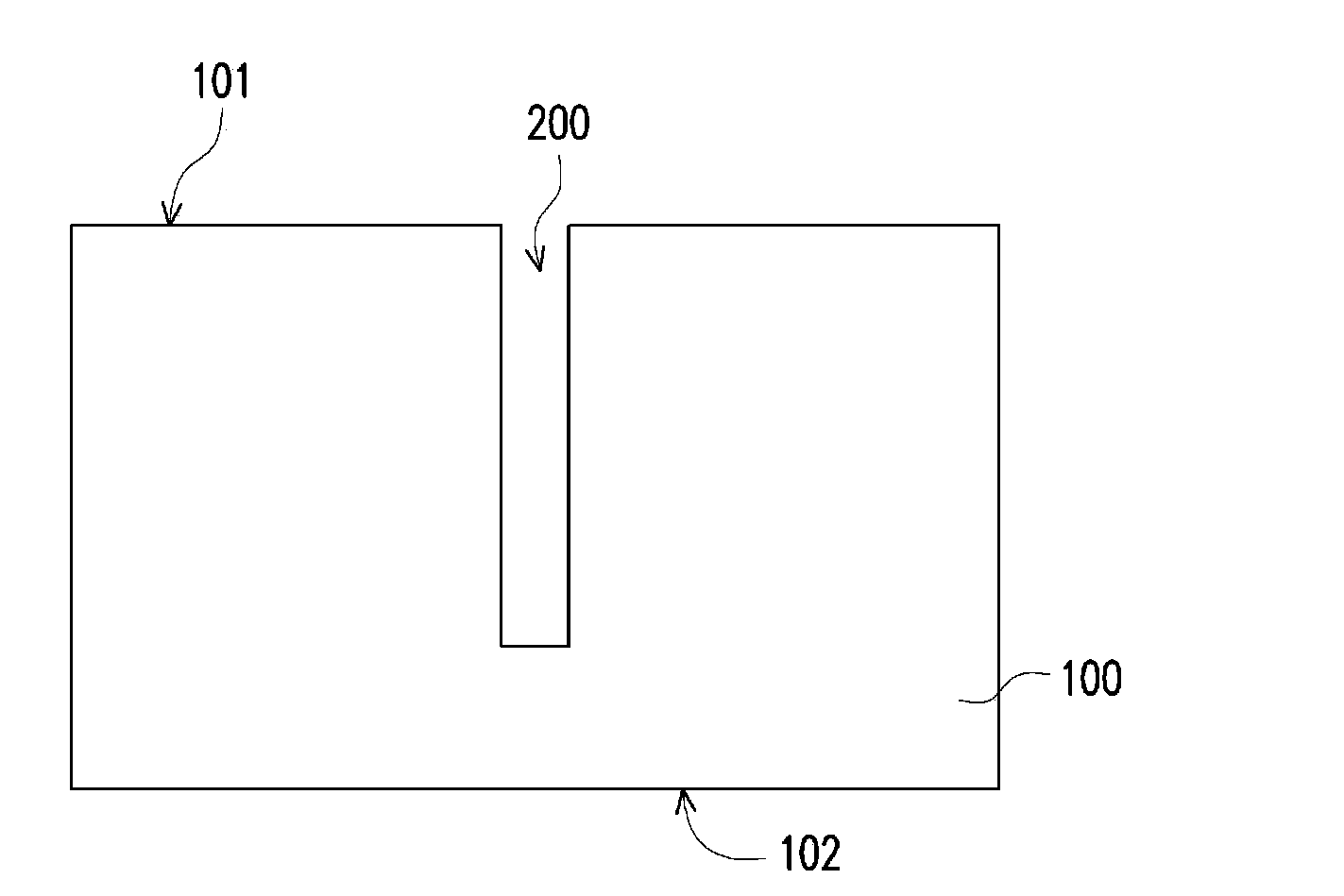

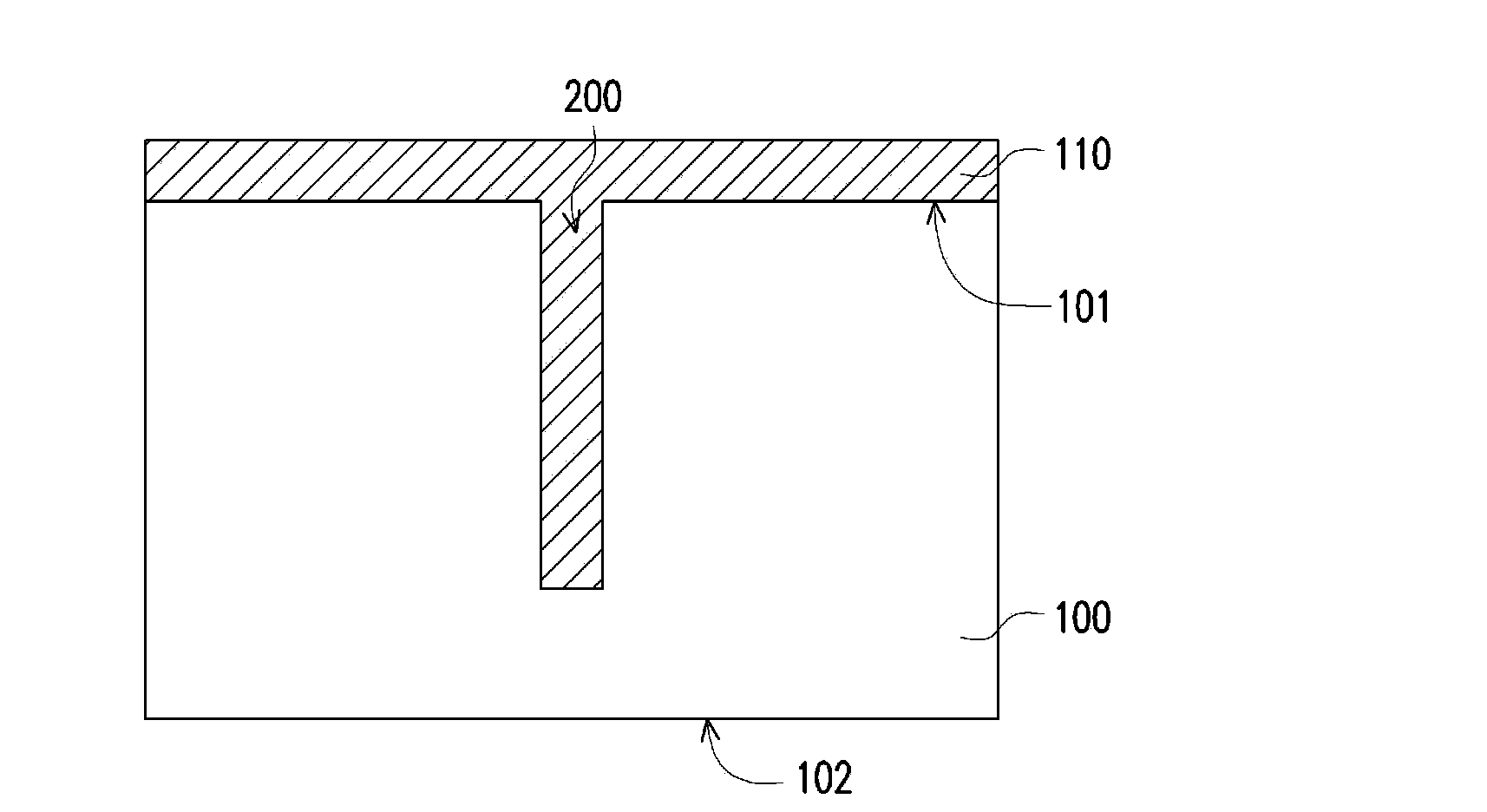

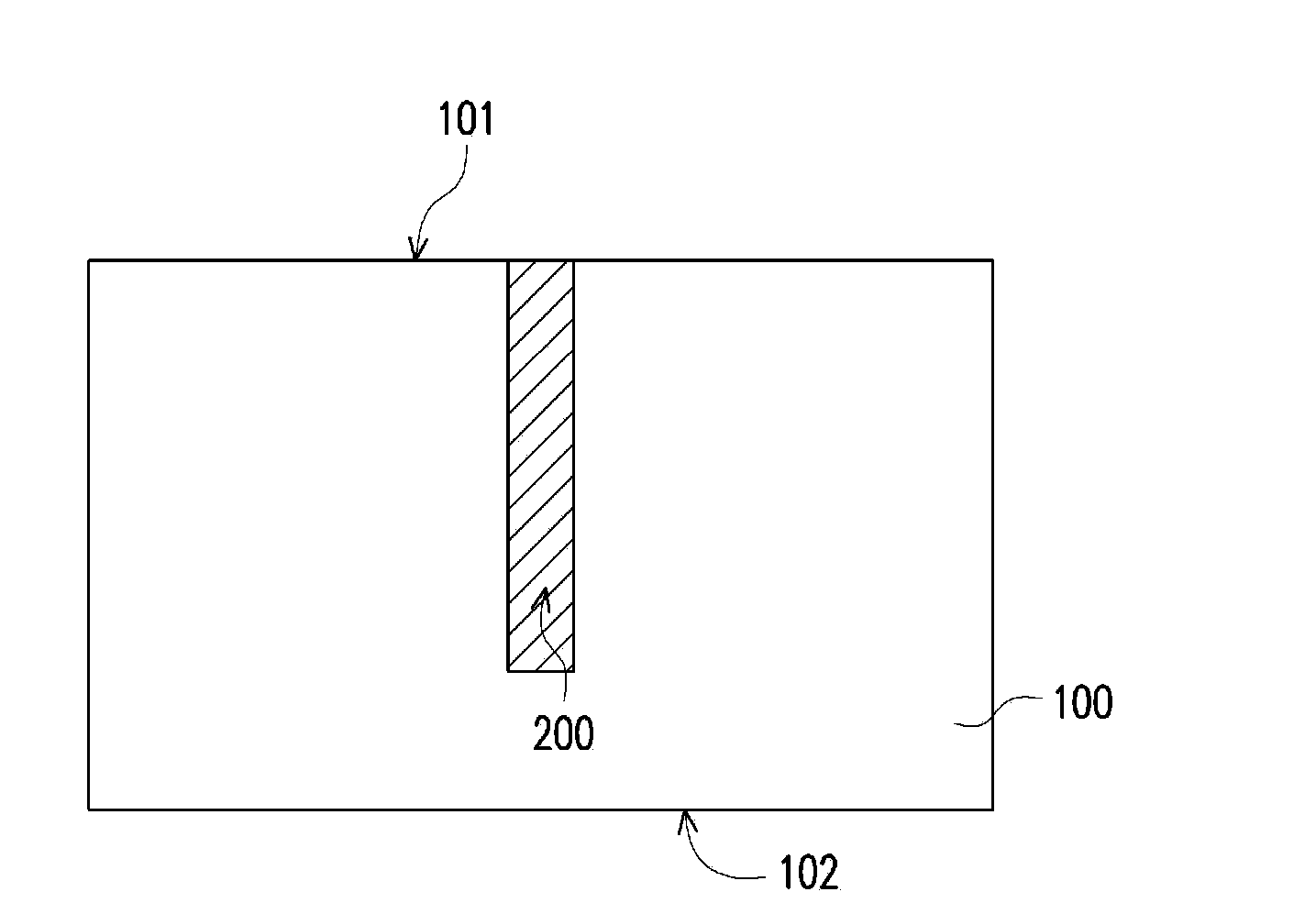

[0058] Figure 1 to Figure 12 is a schematic flow chart of the manufacturing method of the through-substrate structure according to the first embodiment of the present invention. First please refer to figure 1 , a substrate 100 is provided, and the substrate 100 has a first surface 101 and a second surface 102 . According to an embodiment of the present invention, the substrate 100 is, for example, a silicon substrate (such as a wafer) or other suitable semiconductor substrate materials. In general, the first surface 101 of the substrate 100 may be referred to as a back surface, and the second surface 102 of the substrate 100 may be referred to as a top surface. Furthermore, a trench 200 is formed on the first surface 101 of the substrate 100 . Here, the method of forming the trench 200 is, for example, using the photoresist layer on the first surface 101 as an etching mask, and the photoresist layer has an opening at the position of the trench 200 to etch the substrate 100...

no. 2 example

[0073] Figure 14 to Figure 20 is a schematic flowchart of a method for manufacturing a through-substrate structure according to a second embodiment of the present invention. The main difference between the second embodiment and the first embodiment lies in the sequence adjustment of each manufacturing step, so please refer to the above-mentioned first embodiment for details not mentioned here. First please refer to Figure 14 , a substrate 100 is provided, and the substrate 100 has a first surface 101 and a second surface 102 . Moreover, an insulating layer 120 is formed on the first surface 101 of the substrate 100 . In this embodiment, the insulating layer 120 is a three-layer insulating layer formed sequentially, such as a first silicon nitride layer 121 , a first silicon oxide layer 122 and a second silicon nitride layer 123 .

[0074] Please refer to Figure 15 , forming at least one opening on the first surface 101 of the substrate 100 . The embodiment of the prese...

no. 3 example

[0077] Figure 21 to Figure 26 is a schematic flowchart of a method for manufacturing a through-substrate structure according to a third embodiment of the present invention. The main difference between the third embodiment and the above-mentioned first and second embodiments lies in the sequence adjustment of each manufacturing step, so please refer to the above-mentioned first and second embodiments for details not mentioned here. First please refer to Figure 21 , a substrate 100 is provided, and the substrate 100 has a first surface 101 and a second surface 102 . Moreover, an insulating layer 120 is formed on the first surface 101 of the substrate 100 . Then, at least one opening and the trench 200 are simultaneously formed on the first surface 101 of the substrate 100 , and the embodiment of the present invention takes two openings 210 , 220 as an example.

[0078] Please refer to Figure 22 , sequentially form the oxide circuit layer 130 , the barrier layer 140 and th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com