Super-junction power device and manufacturing method thereof

A technology of power devices and conductive types, which is applied in the field of power semiconductor devices, can solve the problems of limited total width of conductive channels, reduce the specific on-resistance of super-junction LDMOS, and achieve low forward conduction resistance, increase width, and reduce resistance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

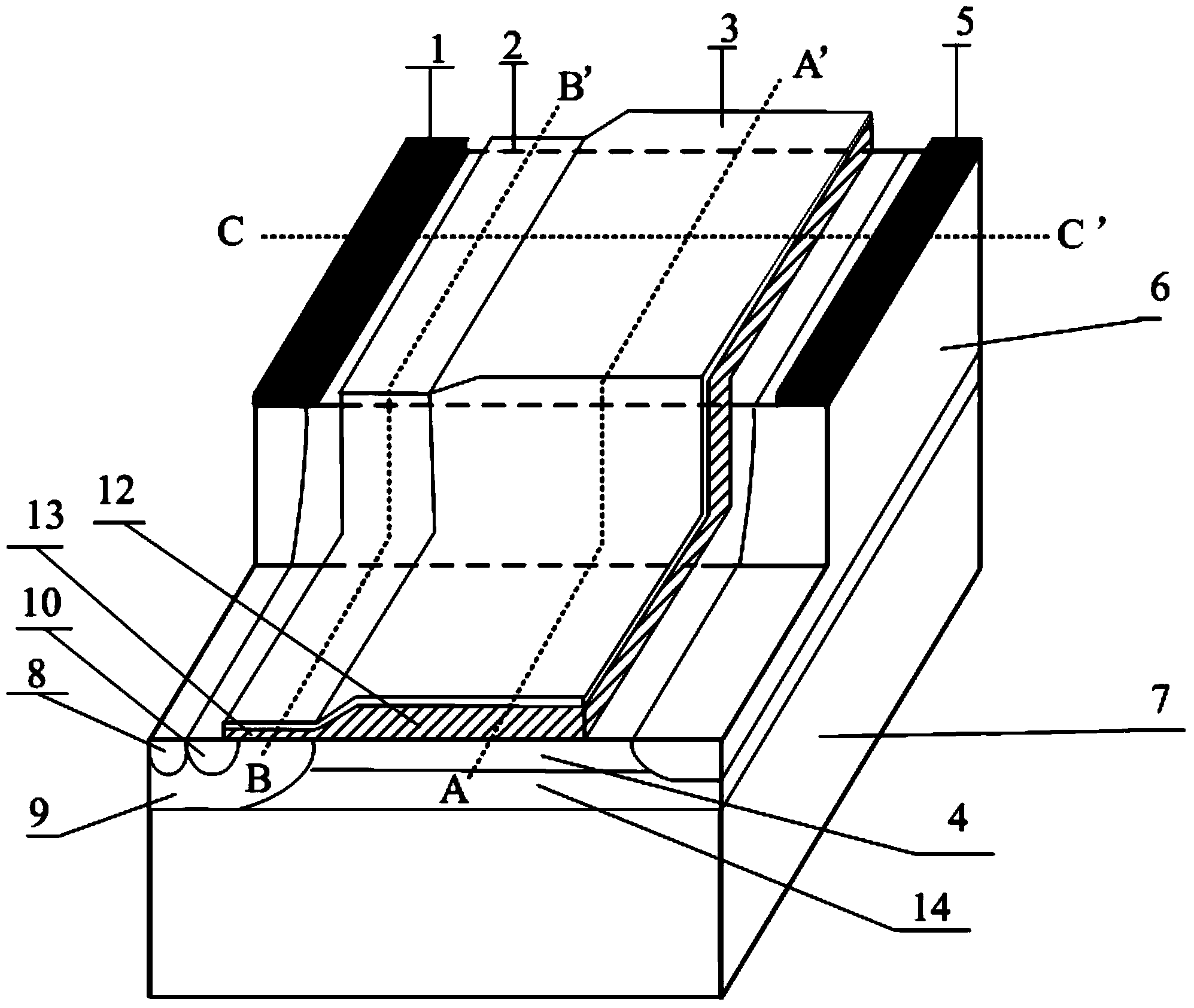

[0038] As a preferred embodiment of the present invention, the present invention discloses a method for preparing a lateral super-junction power device with extremely low specific on-resistance, which includes the following steps:

[0039] (1) Preparation of single crystal silicon, using P-type heavily doped region substrate 1, the doping atoms are arsenic, the concentration is 1.5×10 19 cm -3 , whose crystal orientation is ;

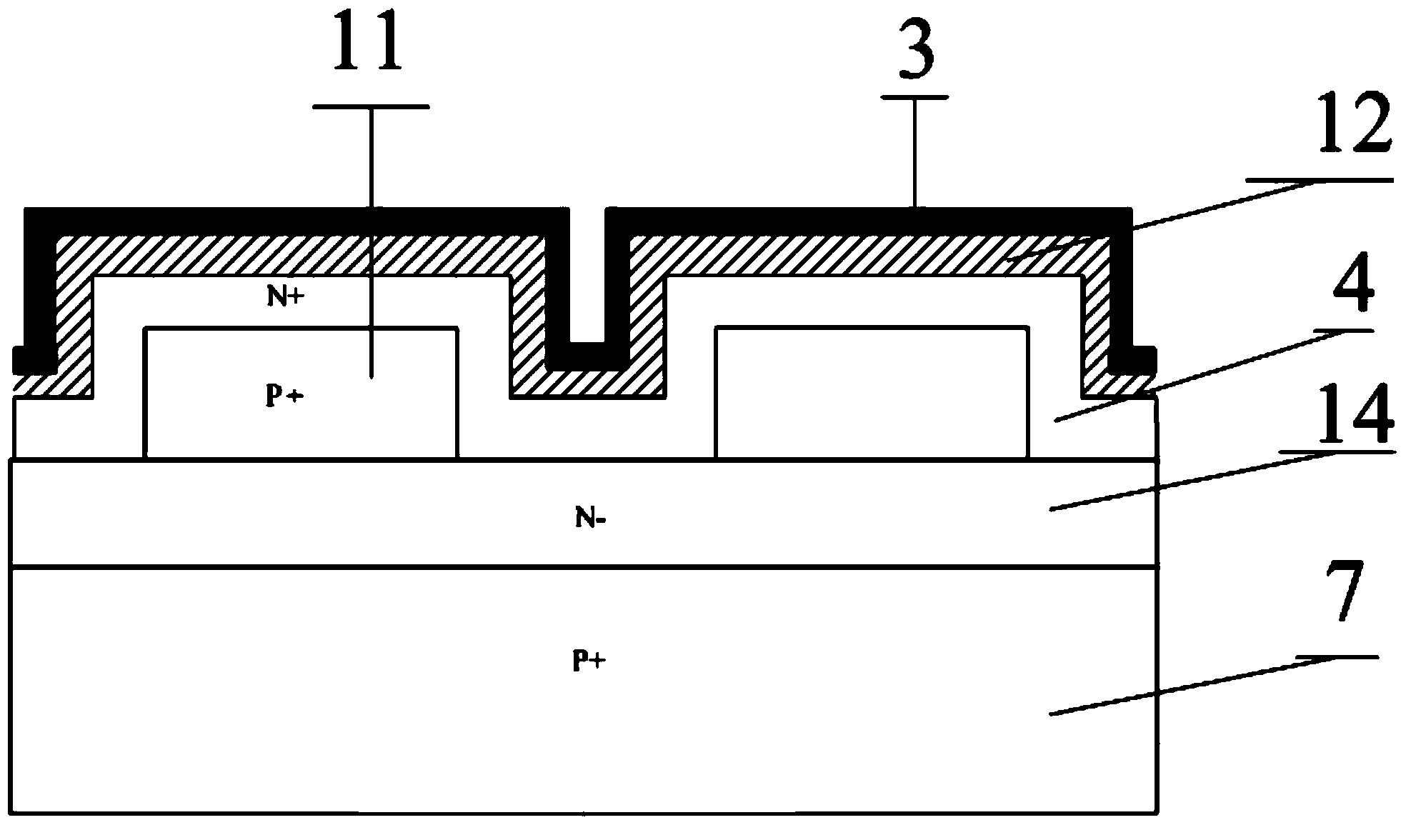

[0040] (2) Epitaxial N- epitaxial layer on P+ substrate, such as Figure 5 As shown in , as the substrate auxiliary depletion layer, the dopant atom is phosphorus, and the epitaxial thickness is adjusted according to the requirements of the device electrical parameters;

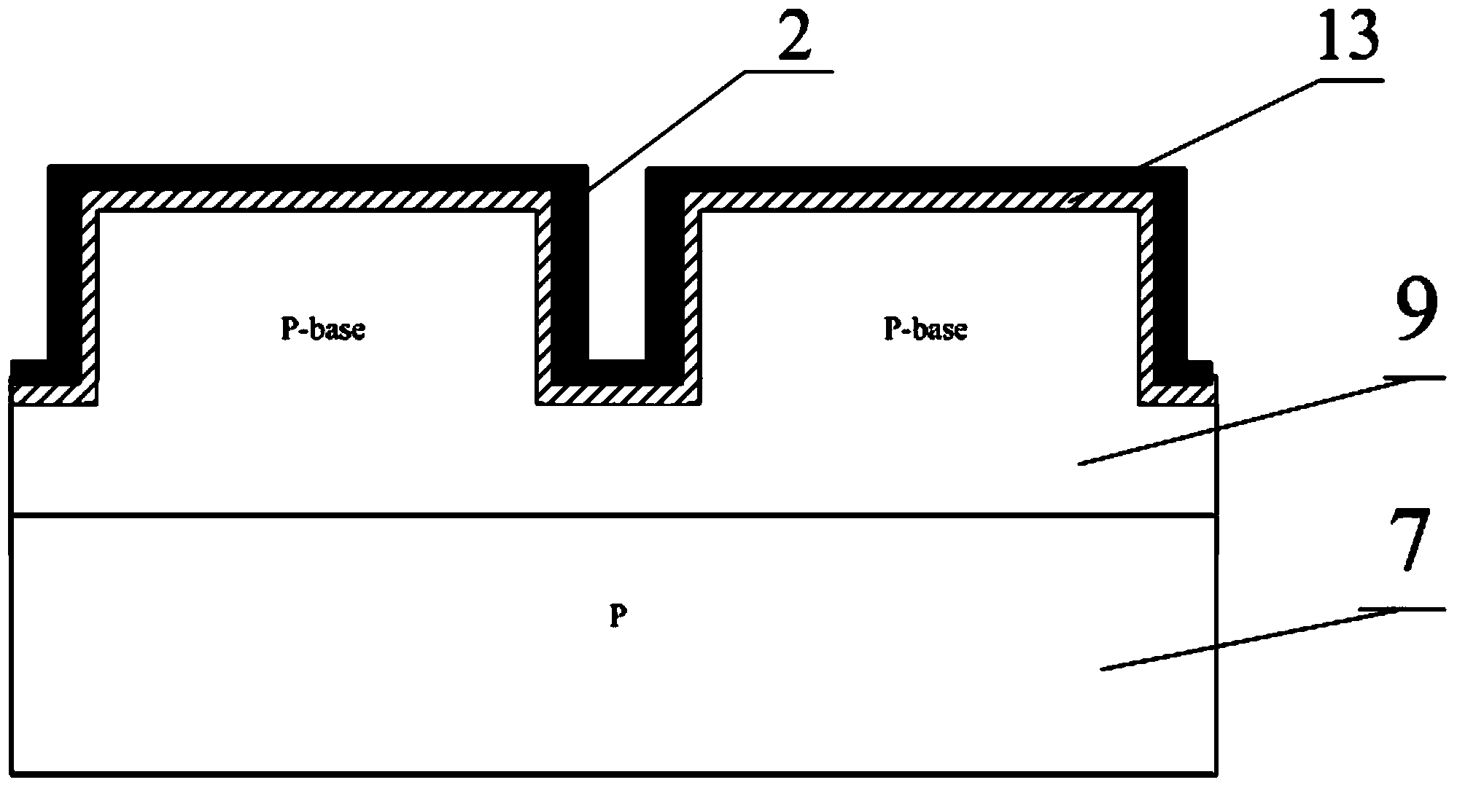

[0041] (3) On the low-resistance N-epitaxial layer, the P-body region and the P-type region are fabricated using boron ion implantation and diffusion processes, such as Figure 6 shown;

[0042] (4) Photolithography, and then use bulk silicon etching to form trench structures in th...

Embodiment 2

[0050] In this example, on the basis of Example 1, the first conductivity type region 11 can also be Figure 5 In the situation shown, part of the region 11 of the first conductivity type remains between the second conductivity type semiconductor auxiliary depletion layer 14 and the second conductivity type semiconductor region 4 at the groove.

[0051] The specific implementation method of embodiment 2 is similar to embodiment 1, except that in the fifth step of the process steps of embodiment 1, the etching depth of the first conductivity type region 11 is reduced, and the first conductive type region 11 of an appropriate thickness is reserved in the trench groove. Conductivity type region 11.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com