Method for extracting trap time constant of gate dielectric layer of semiconductor device

A technology of time constant and gate dielectric layer, applied in semiconductor/solid-state device testing/measurement, instruments, electrical components, etc., can solve problems such as low efficiency, limited test time, and large difference in time constant magnitude

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

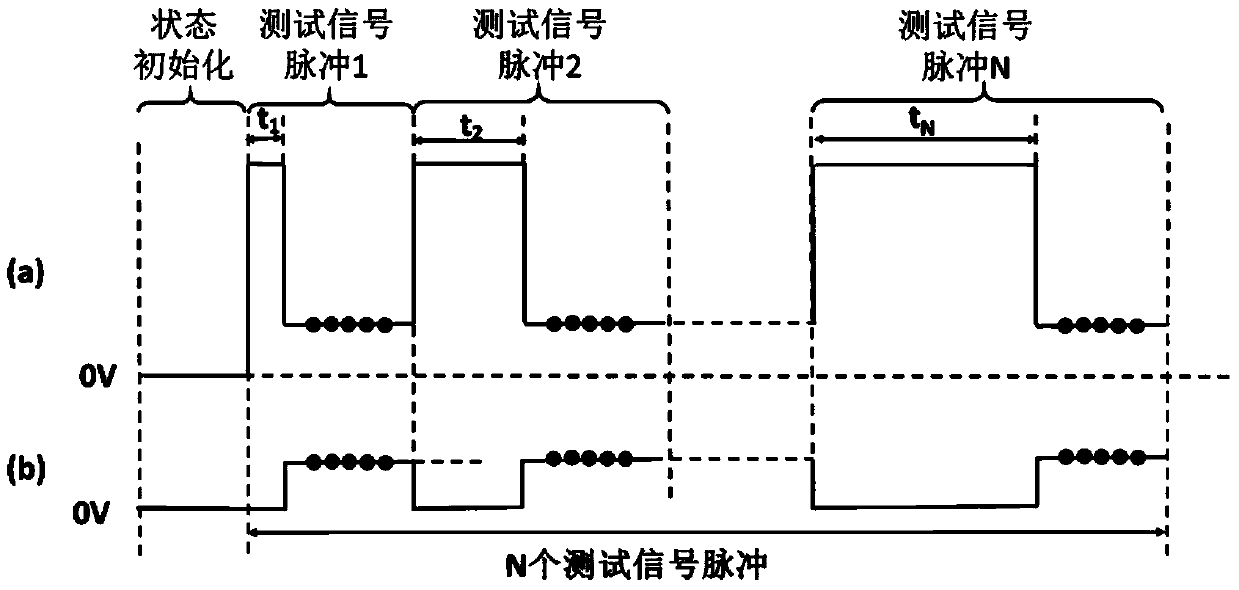

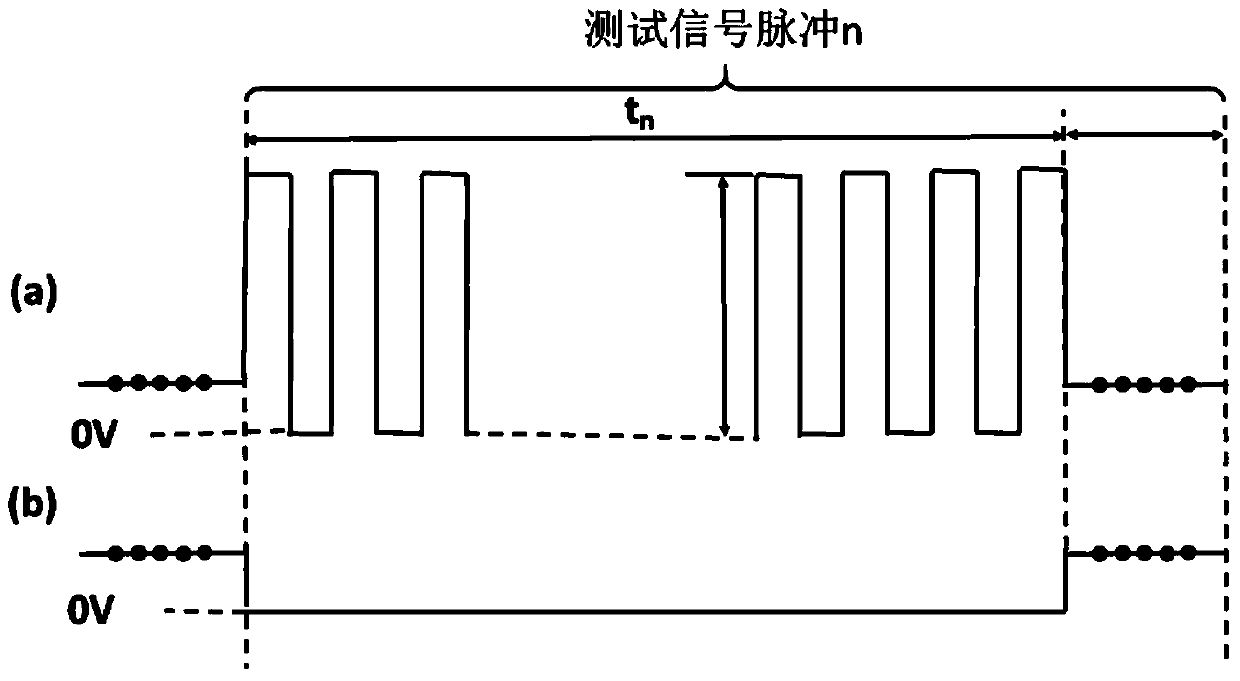

[0029] Below by embodiment and in conjunction with accompanying drawing, describe testing method of the present invention in detail:

[0030] The test steps and data processing methods are as follows:

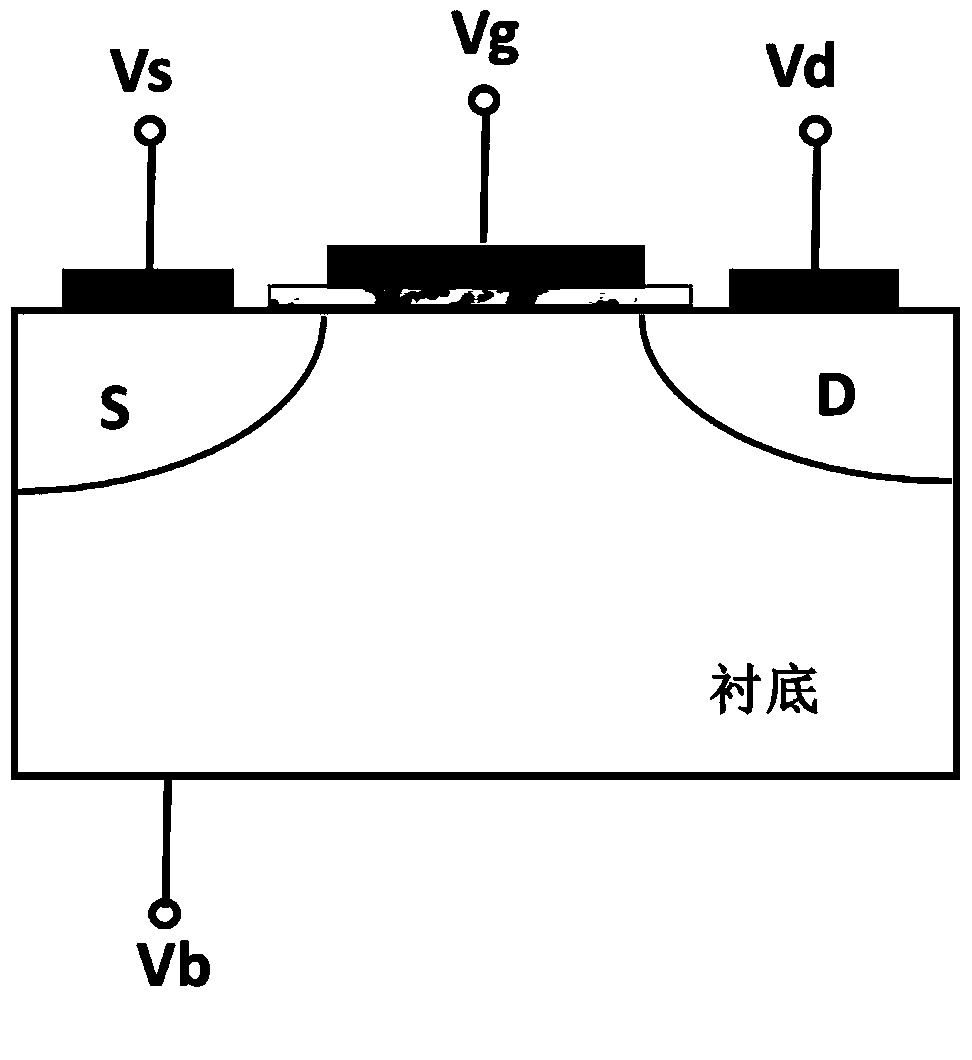

[0031] Test part (the test steps described below are the process of testing and extracting the capture time constant of the N-type device under the DC signal; the source terminal and the body terminal are both grounded during the test, that is, zero bias, probe A and probe B connected to gate terminal and drain terminal respectively):

[0032] 1) The purpose of this step is to initialize the state of the trap so that the trap is in an empty state before applying a high level signal. The drain terminal signal voltage is Vd0, and the gate terminal signal voltage is Vg0. Here, Vd0 and Vg0 are taken as ground signals, that is, zero bias, that is to say, it is necessary to ensure that the device is in a situation without any stress for a sufficient time. The purpose of this step is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com