A chip interface circuit pad driving method and device

A technology of an interface circuit and a driving method, applied in the field of electronic information, can solve the problems of increased inductance effect of the bonding wire, the chip cannot work normally, and the cost of the chip is increased, so as to reduce the cost of the chip, reduce the sso effect, and reduce the voltage change. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] The following will clearly and completely describe the technical solutions in the embodiments of the application with reference to the drawings in the embodiments of the application. Apparently, the described embodiments are only some of the embodiments of the application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

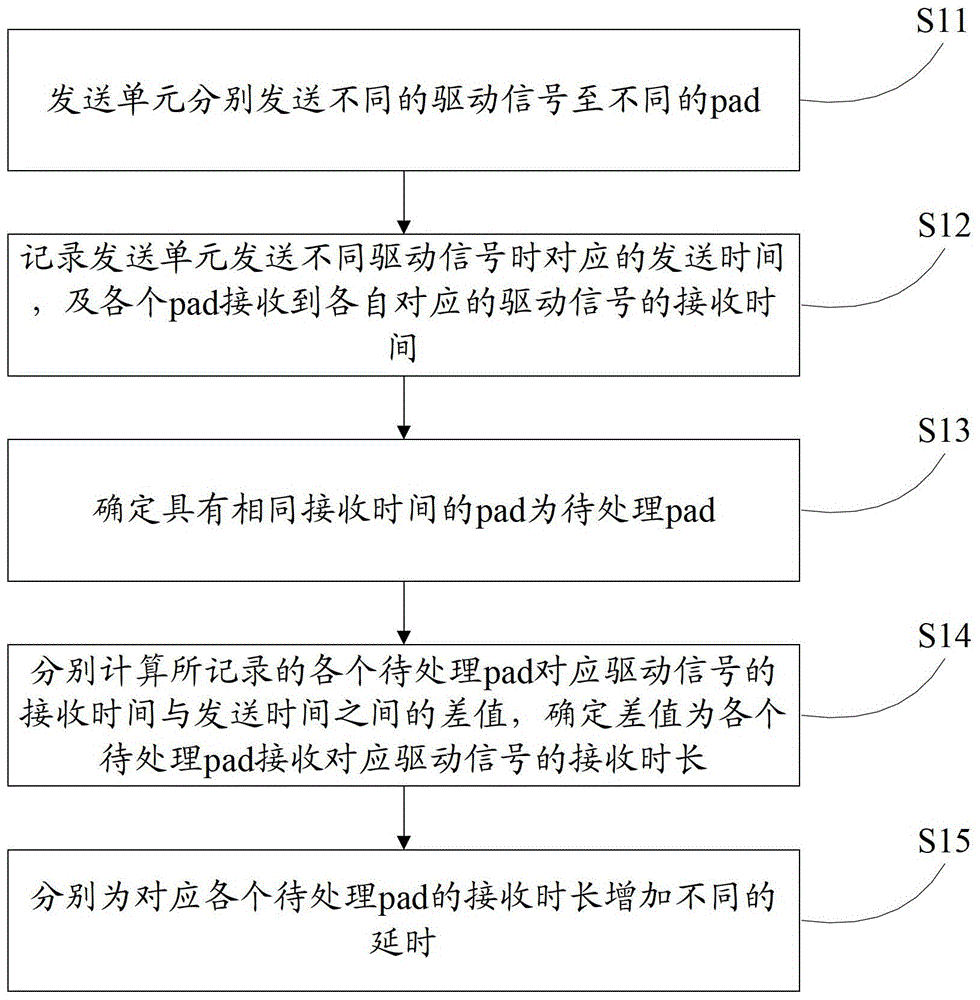

[0060] See figure 1 , which shows a flowchart of a chip interface circuit pad driving method provided by the present application, which may include the following steps:

[0061] Step S11: The sending unit sends different driving signals to different pads respectively.

[0062] In this embodiment, the sending unit is a part of the chip. The pad is the interface circuit of the chip. Since the chip includes a plurality of interface circuit pads of different chips, the sending unit of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com