Address generator of heterogeneous multi-core processor

A multi-core processor and address generator technology, applied in the field of multi-core processors, can solve the problems of inflexible address generation, inability to meet complex algorithm processing requirements, and single address calculation method, so as to improve automatic processing capabilities. , Improve the efficiency of address generation and the effect of expanding the scope of applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

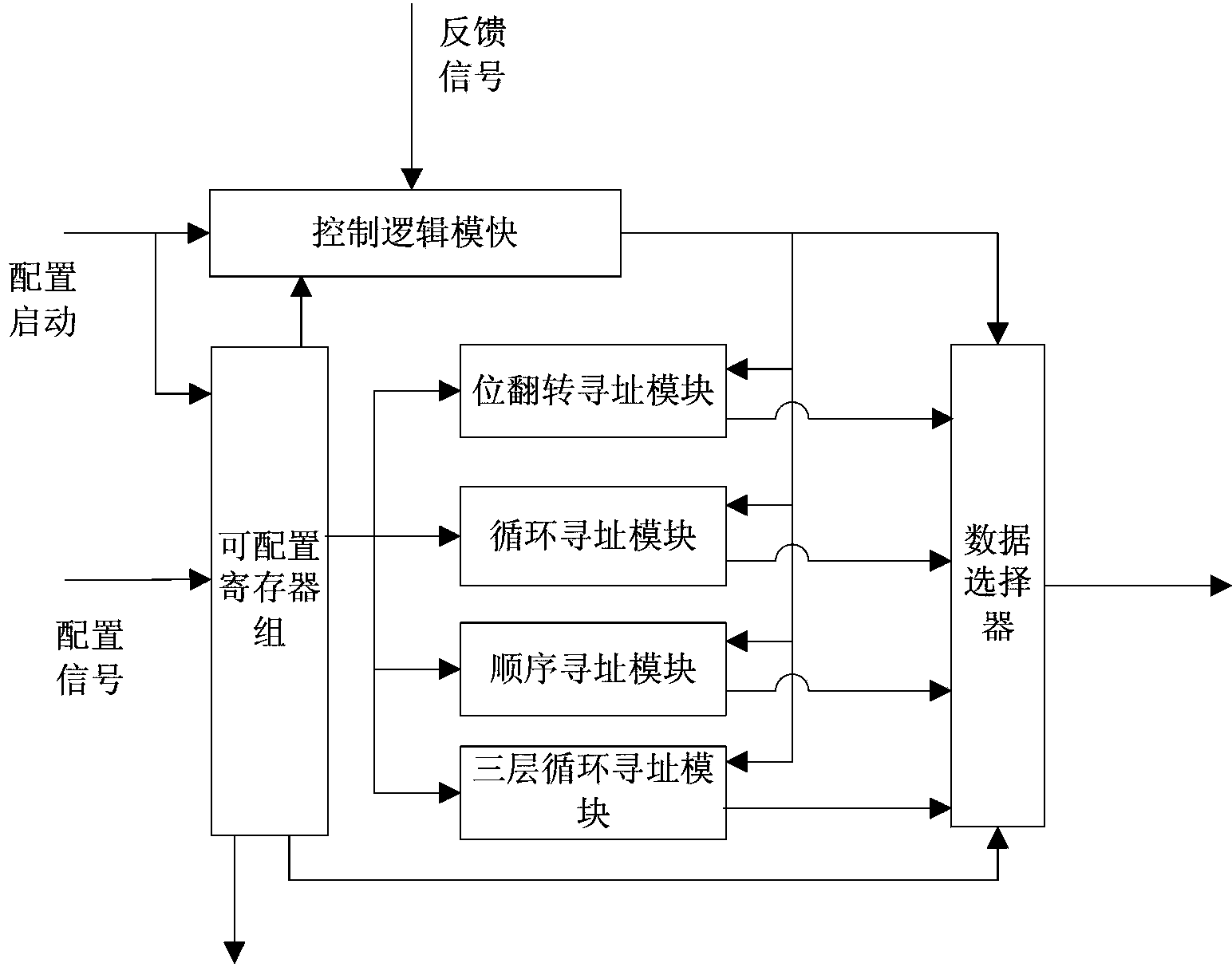

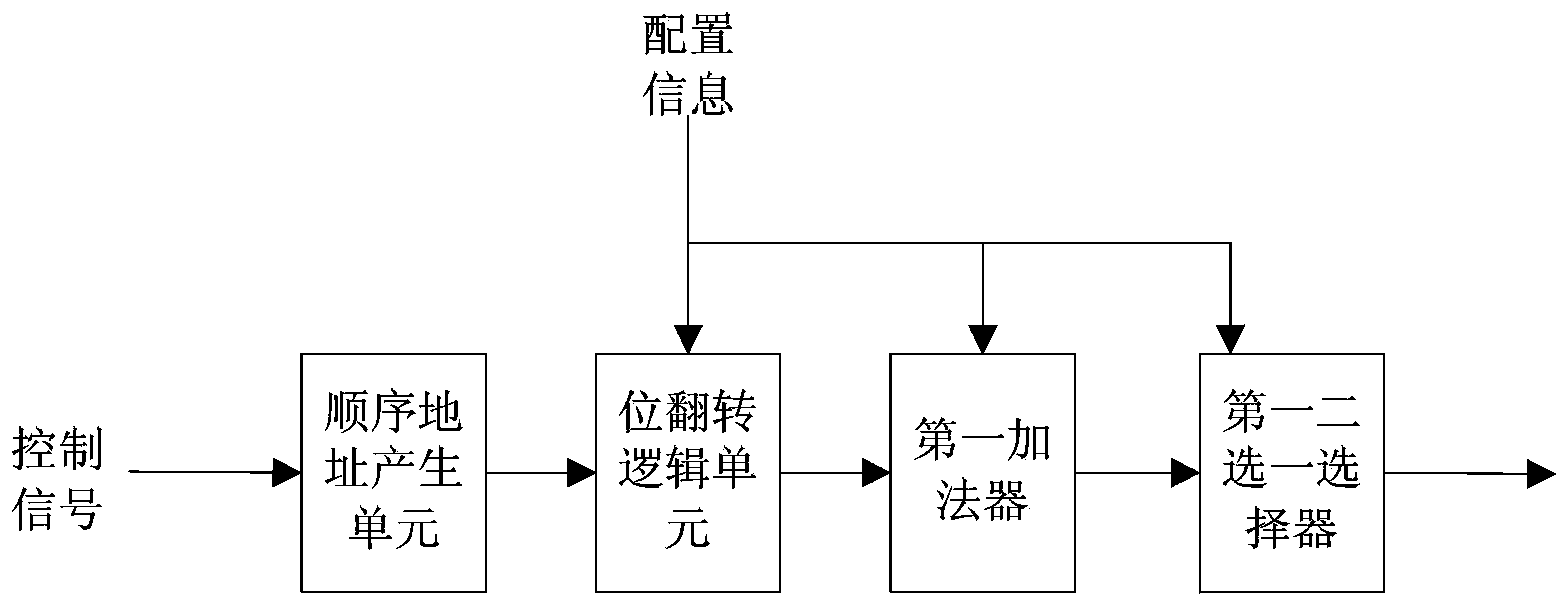

[0057] When heterogeneous multi-core is used for real-time digital signal processing, different algorithms in digital signal processing require different read and write address rules, so the address generator is required to support some complex address generation methods, such as fft operations. The present invention designs a three-layer cyclic address generation method, which can satisfy the addressing of conventional fft operation data and twiddle factors, and can also realize incremental sequential addressing and limited number of cyclic addressing. The address addressing of the three-level loop mode means that the first level of loop is based on the base address and increases according to the configured fixed step size 1 to generate a configured number of addresses; the second level of loop controls the number of cycles of the first level of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com