TFT (thin film transistor) array substrate, and production method thereof and display device

An array substrate and substrate technology, applied in the field of TFT array substrates, TFT array substrate manufacturing methods and display devices, can solve problems such as difficulty in increasing production capacity, achieve the effects of increasing production capacity, avoiding the photoelectric effect, and saving the use of metal materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

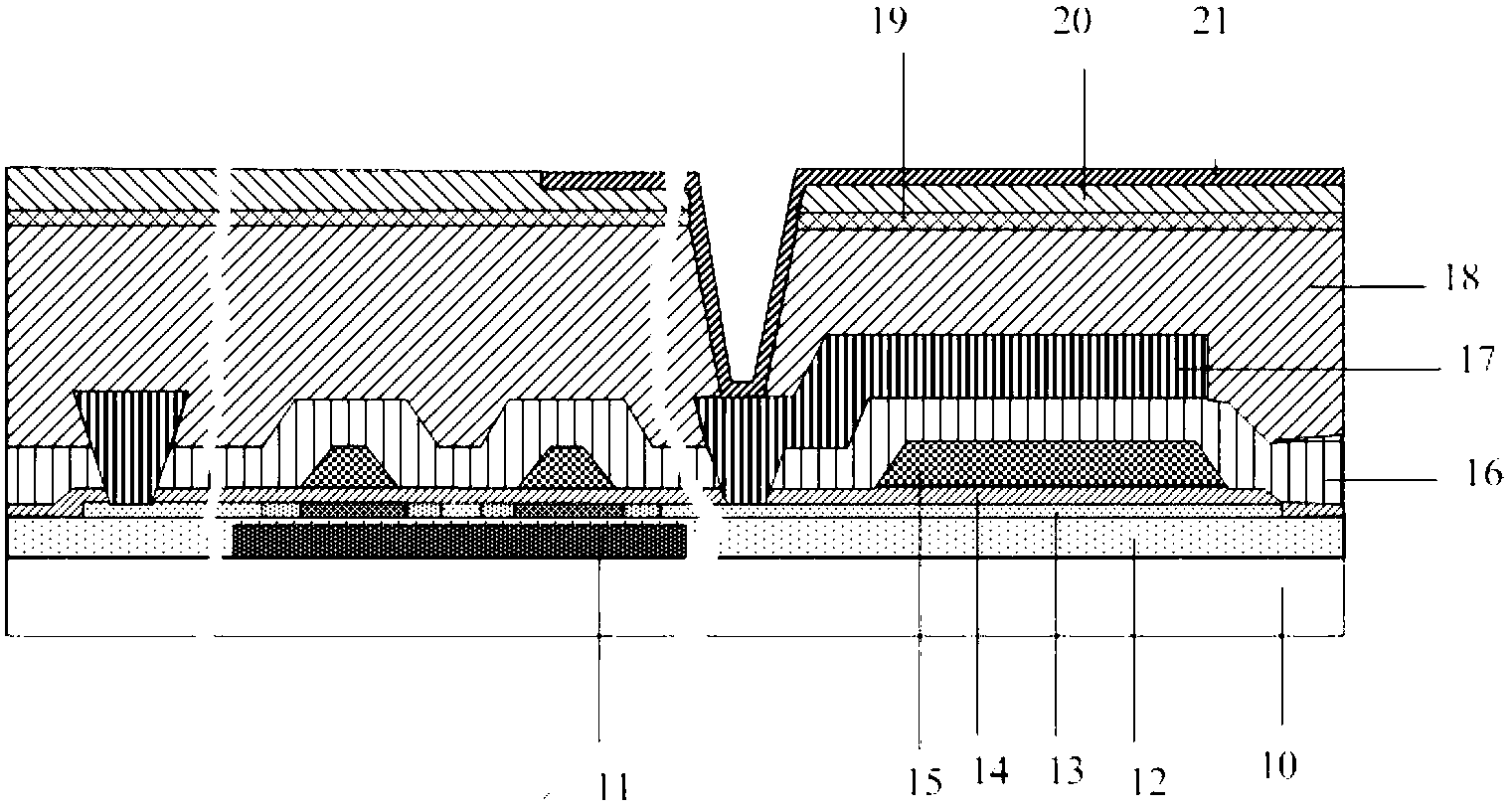

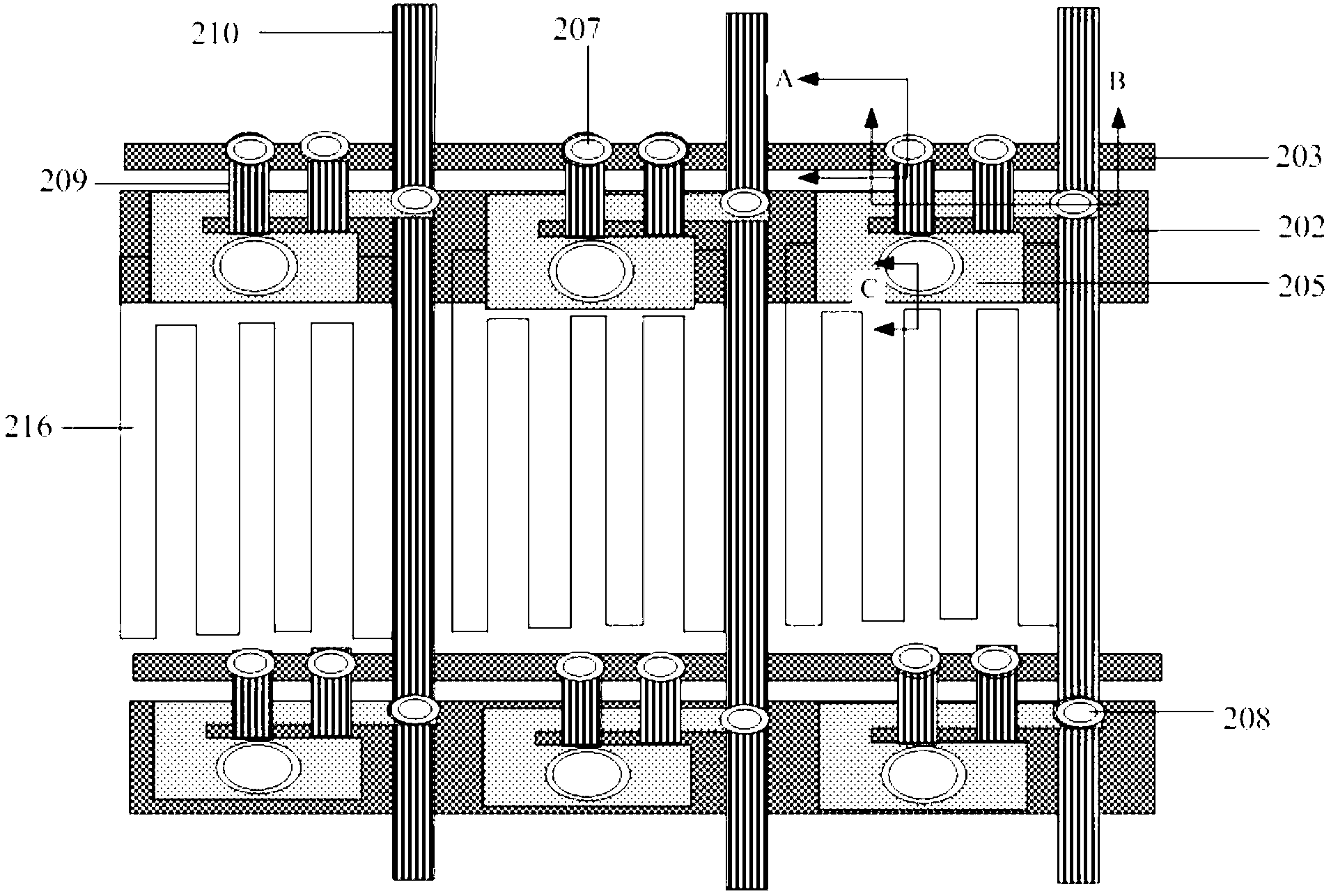

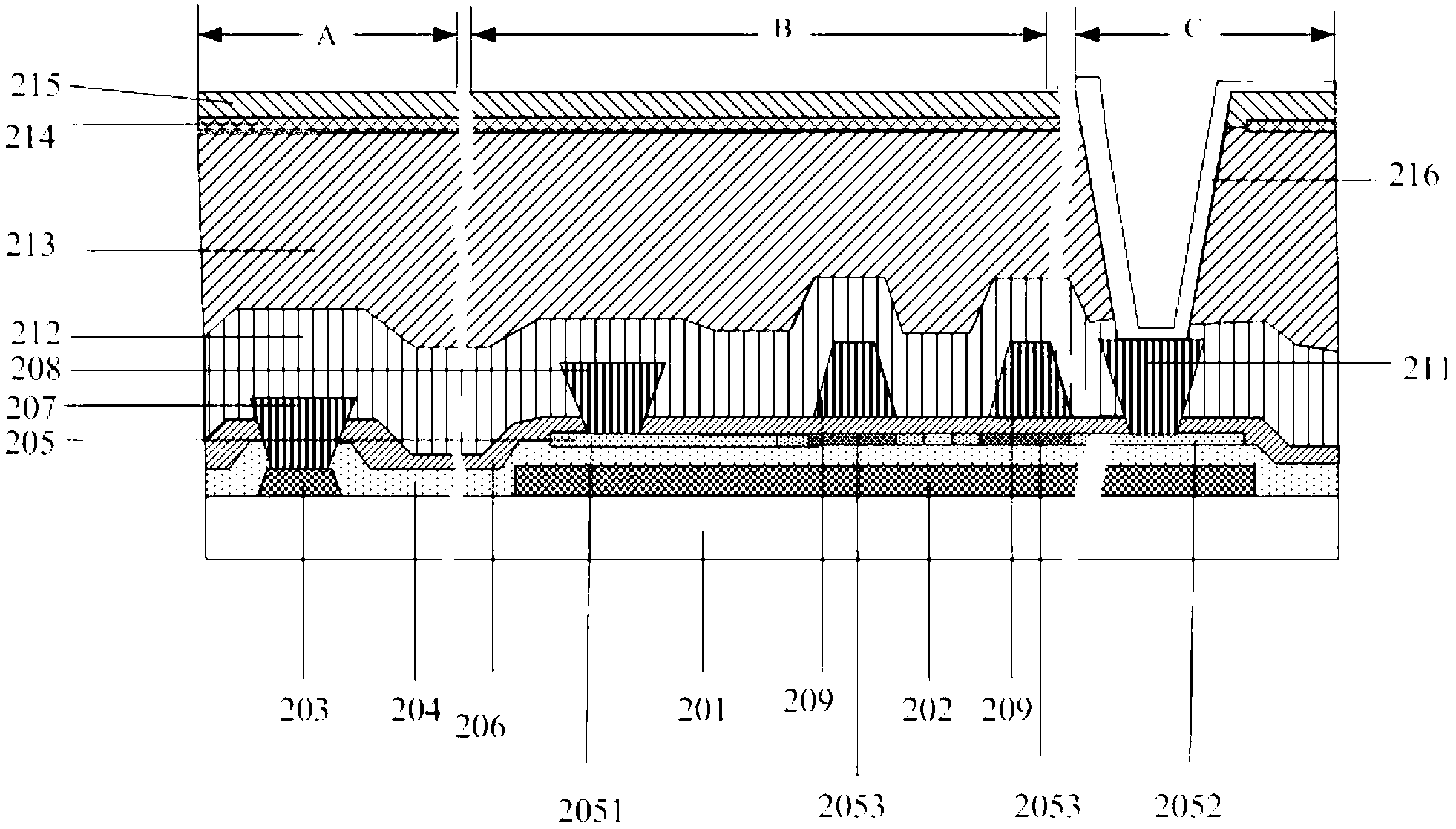

[0095] The first embodiment of the present invention takes the FFS mode as an example to illustrate the structure of the TFT array substrate in the lateral electric field mode. figure 2 with 3 As shown, they are respectively a schematic plan view and a cross-sectional structure view of an FFS mode TFT array substrate provided by the first embodiment of the present invention, in which, figure 2 The three parts A, B, and C correspond to image 3 In parts A, B, and C, the TFT array substrate includes:

[0096] The substrate 201, the common electrode line 202, the gate line 203, the insulating buffer layer 204, the active layer 205, the gate insulating layer 206, the gate lead 207, the source 208, the gate 209 and the data line 210; among them:

[0097] The common electrode line 202 and the gate line 203 extend along a first direction and are formed on the substrate;

[0098] The insulating buffer layer 204 is formed on the common electrode line 202 and the gate line 203;

[0099] The ac...

Embodiment 2

[0128] The second embodiment of the present invention describes the manufacturing method of the FFS mode TFT array substrate in the first embodiment. Such as Figure 5 As shown, it is a schematic flow chart of the manufacturing method of the TFT array substrate according to the second embodiment of the present invention, including the following steps:

[0129] Step 101: At Figure 6a The first metal layer is deposited on the substrate shown, and formed by a mask process such as Figure 6b As shown in the common electrode lines and gate lines extending in the first direction, the first metal layer is opaque.

[0130] Step 102: Deposit an insulating buffer layer and an amorphous silicon layer sequentially on the substrate on which the common electrode line and the gate line are formed, and form an active layer on the amorphous silicon layer through an excimer laser thermal annealing process, a mask process, and a doping process The active layer includes a source region, a drain regio...

Embodiment 3

[0168] The third embodiment of the present invention uses the TN mode as an example to illustrate the structure of the TFT array substrate in the lateral electric field mode. figure 2 with Picture 9 As shown, they are respectively a schematic plan view and a schematic cross-sectional structure view of a TN mode TFT array substrate provided in the third embodiment of the present invention, in which, figure 2 The three parts A, B, and C correspond to Picture 9 In parts A, B, and C, the TFT array substrate includes:

[0169] The substrate 201, the common electrode line 202, the gate line 203, the insulating buffer layer 204, the active layer 205, the gate insulating layer 206, the gate lead 207, the source electrode 208, the gate 209 and the data line 210; among them:

[0170] The common electrode line 202 and the gate line 203 extend along a first direction and are formed on the substrate;

[0171] The insulating buffer layer 204 is formed on the common electrode line 202 and the ga...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com