Memory and its column decoding circuit

A memory and column decoding technology, which is applied in the field of memory and its column decoding circuit, can solve the problems of large memory power loss, etc., and achieve the effects of reducing power loss, reducing power loss, and reducing the amount of charge

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

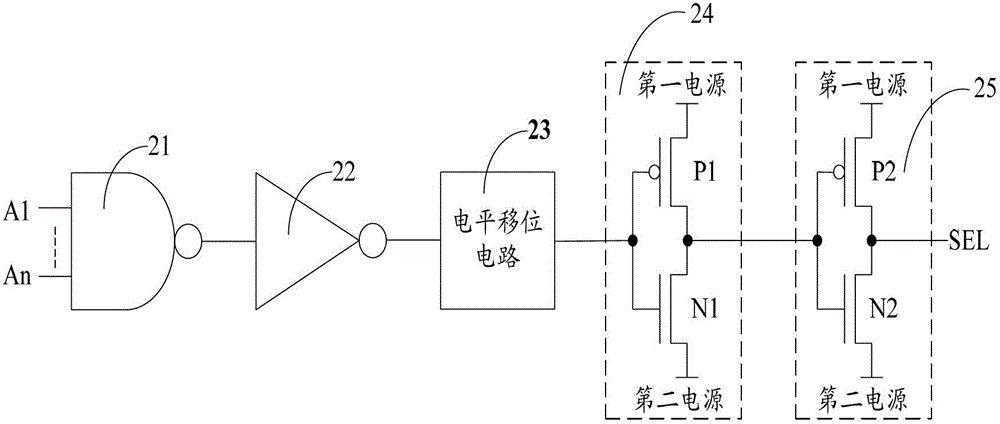

[0044] Figure 4 It is a structural schematic diagram of the column decoding circuit of the memory according to Embodiment 1 of the present invention. refer to Figure 4 The column decoding circuit of the memory includes a NAND gate circuit 41 , a NOT gate circuit 42 , a level shift circuit 43 and a first drive circuit 44 connected in sequence, and also includes a second drive circuit 45 and a precharge circuit 46 .

[0045] The second driving circuit 45 includes a first PMOS transistor P1, a first NMOS transistor N1 and a second NMOS transistor N2. The source of the first PMOS transistor P1 is adapted to be connected to a first power supply, the gate of the first PMOS transistor P1 is connected to the gate of the first NMOS transistor N1, and the drain of the first PMOS transistor P1 is connected to The drain of the first NMOS transistor N1, the source of the first NMOS transistor N1 is connected to the drain of the second NMOS transistor N2, and the gate of the second NMOS...

Embodiment 2

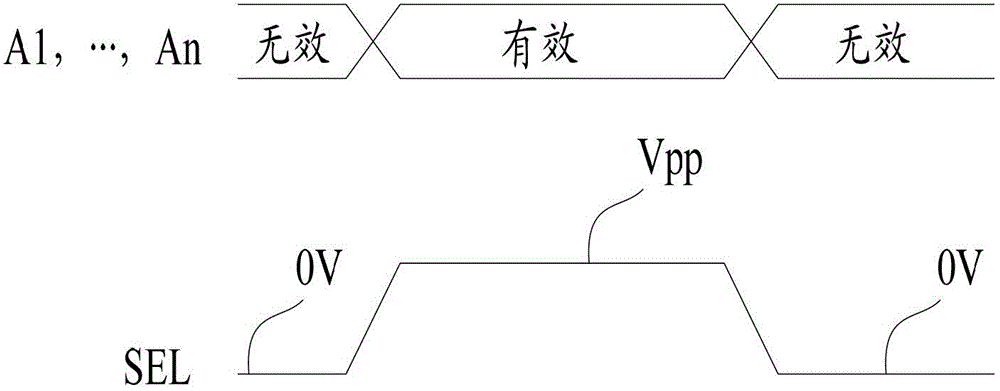

[0072] As described in Embodiment 1, when it is necessary to perform a write operation on the storage column controlled by the column decoding circuit, the amplitude of the column selection signal SEL rises from 0V to 7V-9V; When the storage column controlled by the decoding circuit performs a write operation, the amplitude of the column selection signal SEL drops from 7V-9V to 0V. During the rising and falling process of the amplitude of the column selection signal SEL, if the rate of change of the amplitude of the column selection signal SEL is too fast, it is easy to cause the transistors in the first driving circuit 44 and the second driving circuit 45 to generate Latch up (latch up) effect, resulting in transistor damage.

[0073] In order to solve the above problems, the technical solution of the present invention also provides Embodiment 2. Figure 7 It is a structural schematic diagram of the column decoding circuit of the memory according to Embodiment 2 of the prese...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com