USB (Universal Serial Bus) chip silicon wafer level automatic test device and test method

A technology of silicon wafer level and tester, which is applied in the field of USB chip silicon wafer level tester and USB chip silicon level tester, can solve the problems that the response signal processing of the USB chip cannot be realized, so as to reduce the test cost and improve the same test number, the effect of avoiding test errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

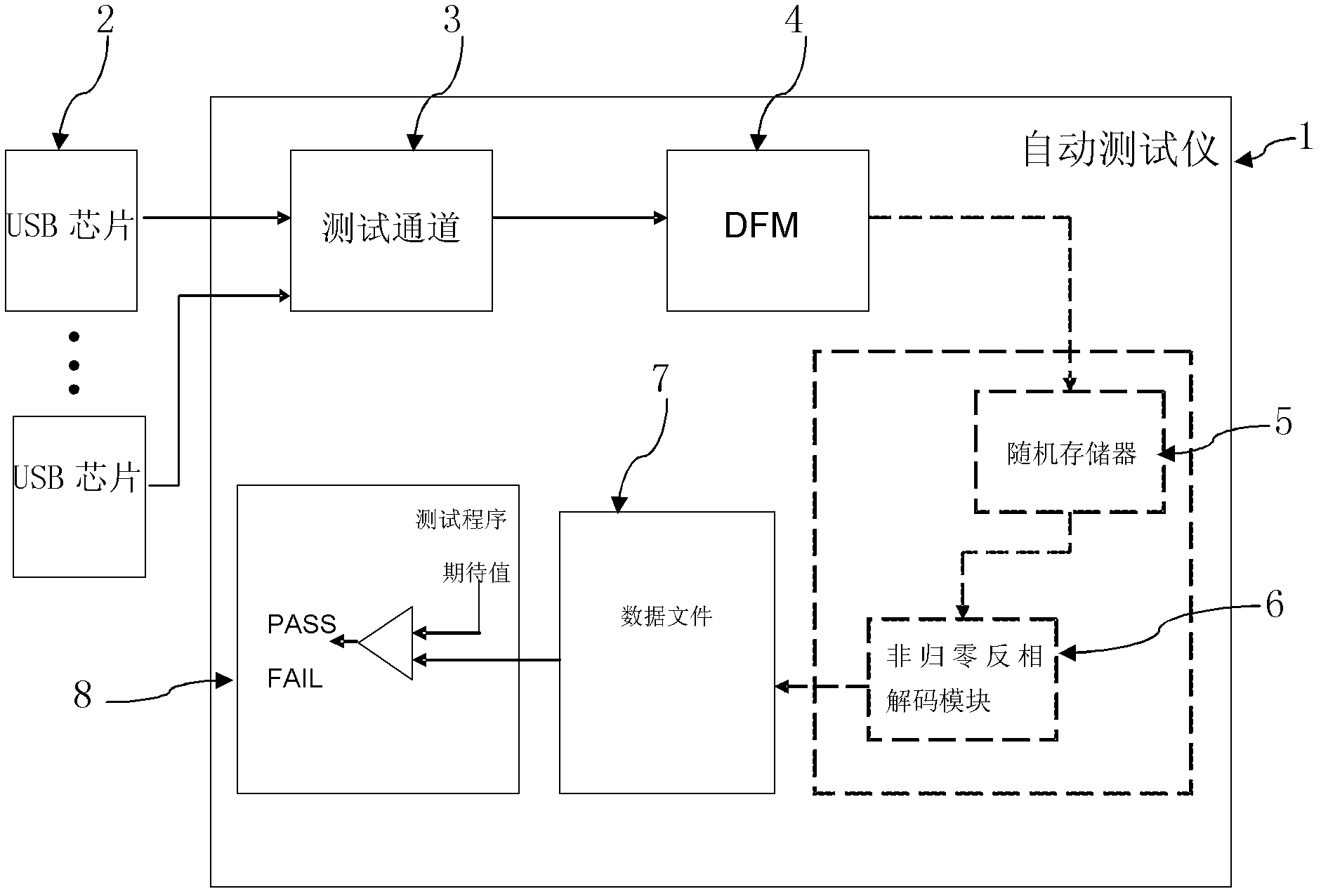

[0033] Such as image 3 As shown, it is a schematic diagram of a silicon-level automatic tester for a USB chip according to an embodiment of the present invention. The embodiment of the present invention USB chip silicon chip level automatic tester 1 is used for the silicon chip level test of USB chip 2, comprises: test channel 3, failure data memory 4, random access memory 5, non-return-to-zero inversion decoding module 6, data file 7 and test procedure 8.

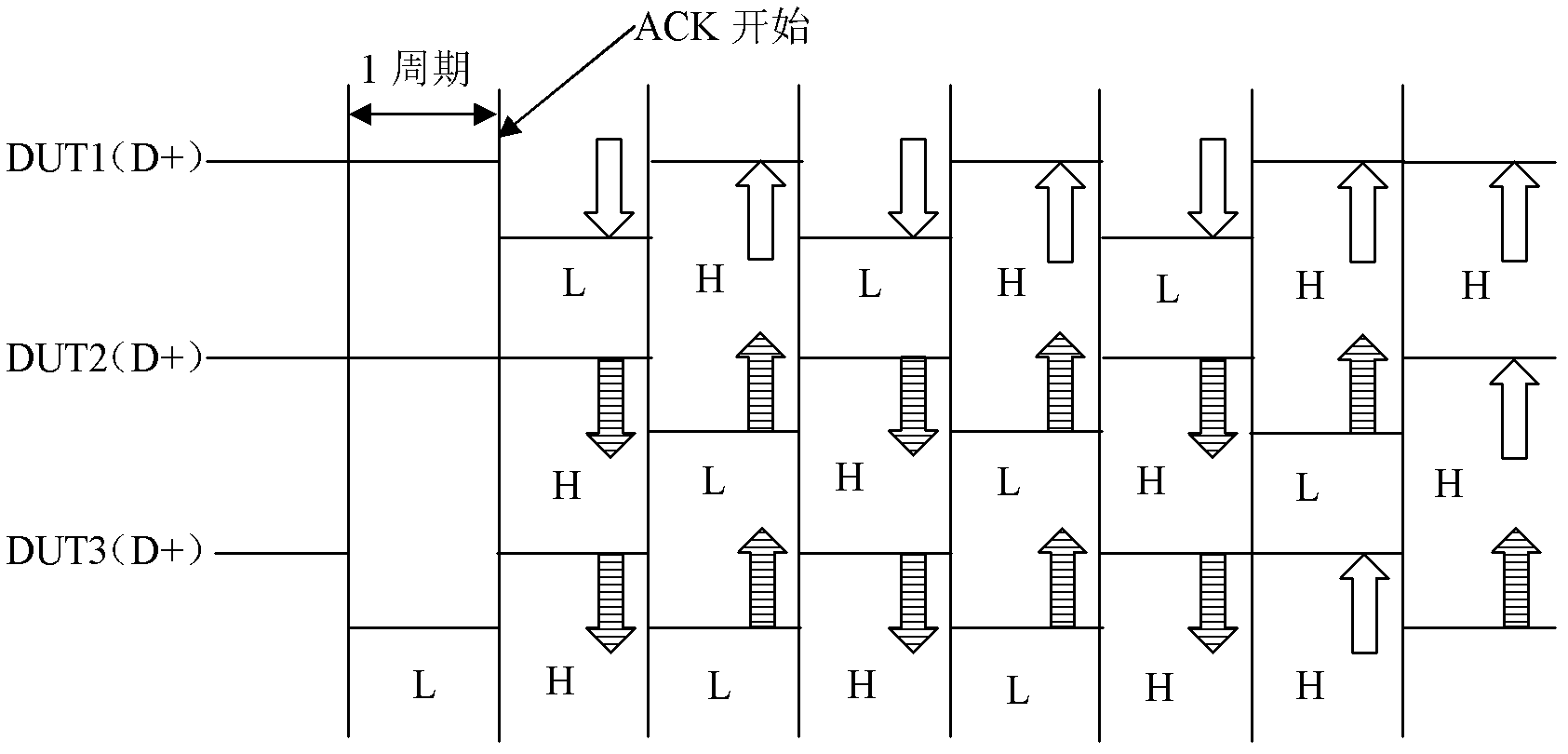

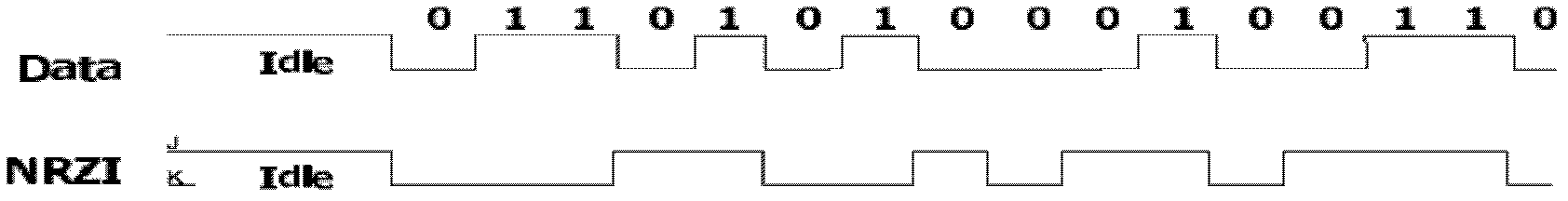

[0034] The test channel 3 includes multiple and is used to connect with one or more USB chips 2, wherein every two test channels are connected to one of the USB chips 2, and the test channel is used to receive each of the USB chips 2 The returned handshake response signal or data. The DP signal pin and the DM signal pin of each USB chip 2 are respectively connected to one of the test channels 3 . The handshake response signal or data handshake response signal includes ACK, NAK, STALL, and the data flow type of the hand...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com