Embedded motor and load power level simulation system

A load power, simulation system technology, applied in simulators, general control systems, control/regulation systems, etc., can solve problems such as motor destructiveness, unfavorable fault control, and unseen problems, and achieve high precision and strong adaptability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

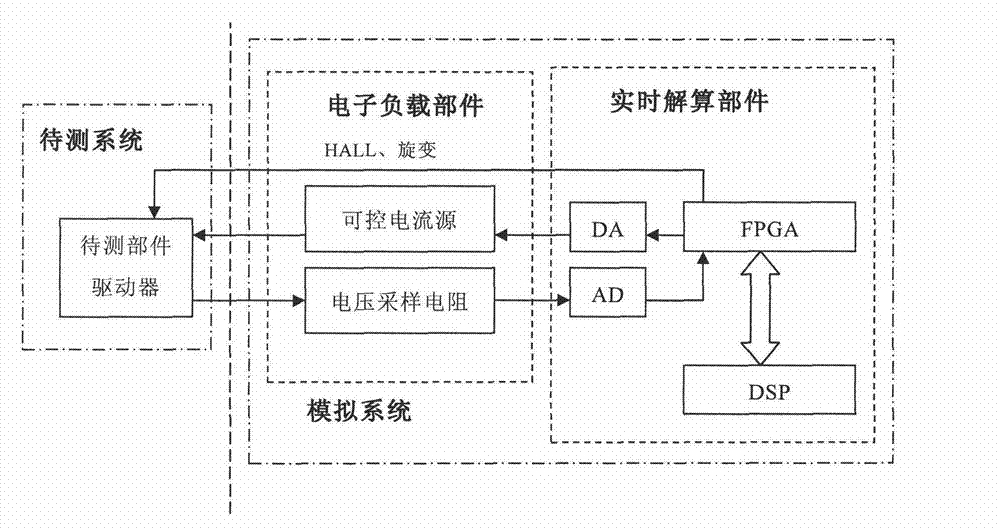

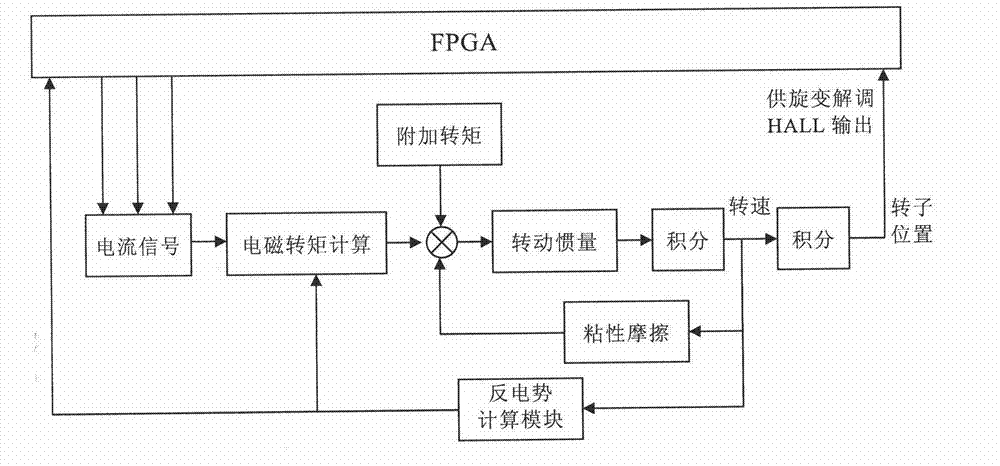

[0033] The invention provides an embedded motor and load power level simulation system, which can realize the signal level simulation of the motor, the dynamic power level simulation of the motor load, and the simulation and control of the motor fault state, so as to meet the needs of motor control and drive. The test coverage requirements of the circuit provide a basis for the design of the motor and mechanism.

[0034] In order to solve the problem of verifying the functional performance of the motor control drive circuit, the simulation system involved in the present invention adopts an embedded design to simulate the power level of the motor and its load. It is mainly composed of a real-time control calculation module, an electronic load module and an input and output circuit. The real-time control and calculation part adopts the architecture of DSP+FPGA, which is responsible for the real-time calculation of the motor and load model; the electronic load is mainly composed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com