Equipment port failure detecting and positioning method and equipment port failure detecting and positioning system

A fault detection and device port technology, applied in the field of network communication, can solve the problems of reducing the efficiency of port fault detection and positioning, reducing the fineness of port fault detection and positioning, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

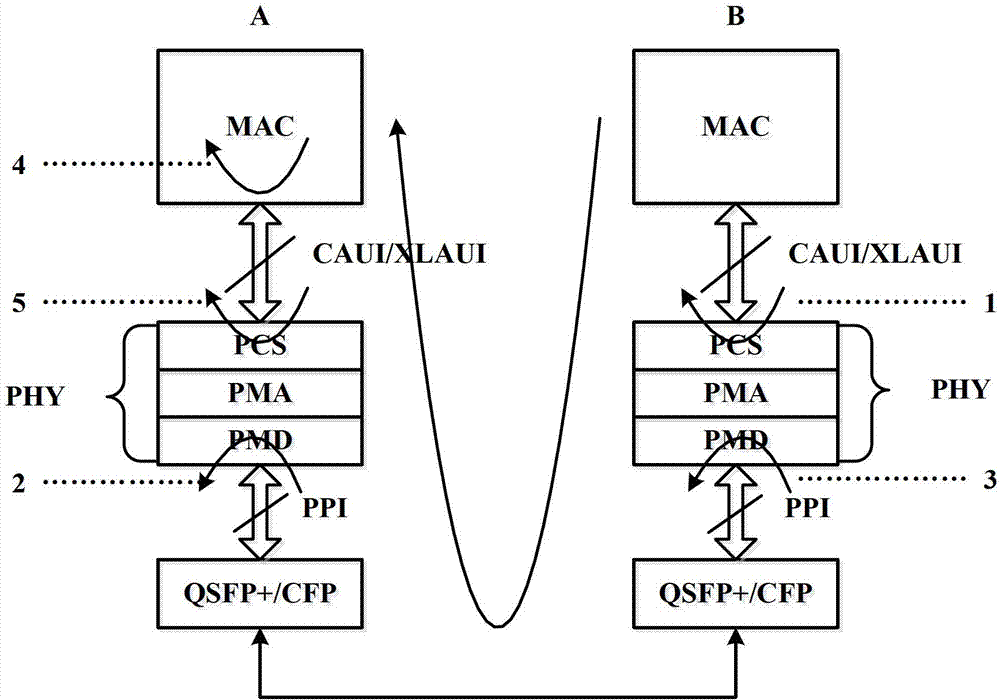

[0029] In the embodiment of the present invention, the self-loop function of the chip is used to detect port faults, and the following combination figure 2 Introduce the self-loop function of each chip.

[0030] 1. MAC self-loop: Take the self-loop function of the MAC chip of port A as an example. Under normal conditions, when port A sends a data packet to port B, the processing flow of the data packet is: MAC chip-AUI interface-PHY chip ( The sequence is PCS sublayer-PMA sublayer-PMD sublayer)-PPI interface-physical transmission medium-port B, when port A starts the MAC chip self-loop function, the data message sent by port A will be returned directly at the MAC chip For the MAC chip processing of port A, such as figure 2 Action 4 in;

[0031] 2. PCS self-loop: Take port B sending data packets to port A as an example. Under normal conditions, the internal data packet processing process of port B is: MAC chip-PCS sublayer-PMA sublayer-PMD sublayer. After port B starts the...

Embodiment 2

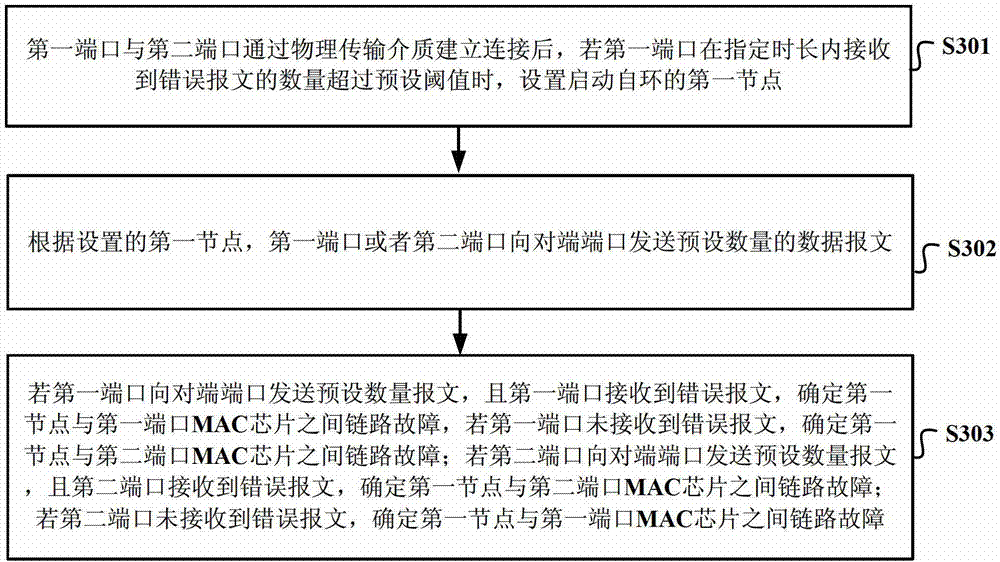

[0043] During specific implementation, when the determined faulty link contains multiple nodes, the method provided according to Embodiment 1 cannot accurately locate the faulty chip, thus reducing the fineness of port fault detection. Therefore, in order to further improve the fineness of fault detection, preferably, in the embodiment of the present invention, the following steps may also be included:

[0044] A1. The two nodes at both ends of the determined faulty link are set to be node A and node B respectively, wherein the distance between the node A and the first port is smaller than the distance between the node B and the first port;

[0045] Taking the first node as the PCS as an example, assuming that the link fault between the PCS and the MAC chip of the first port is determined, after the faulty link is determined, it can be determined that the two ports of the faulty link are respectively the MAC chips of the first port. Chip and PCS, set node A as the first port M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com