Reset method of internal memory of chip based on scan chain

A reset method and register technology, applied in electrical components, pulse technology, electronic switches, etc., can solve the problems of asynchronous reset structure stability, difficulty in chip design and implementation, and difficulty in chip physical implementation, so as not to affect data path performance, Does not affect chip performance, easy to achieve effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

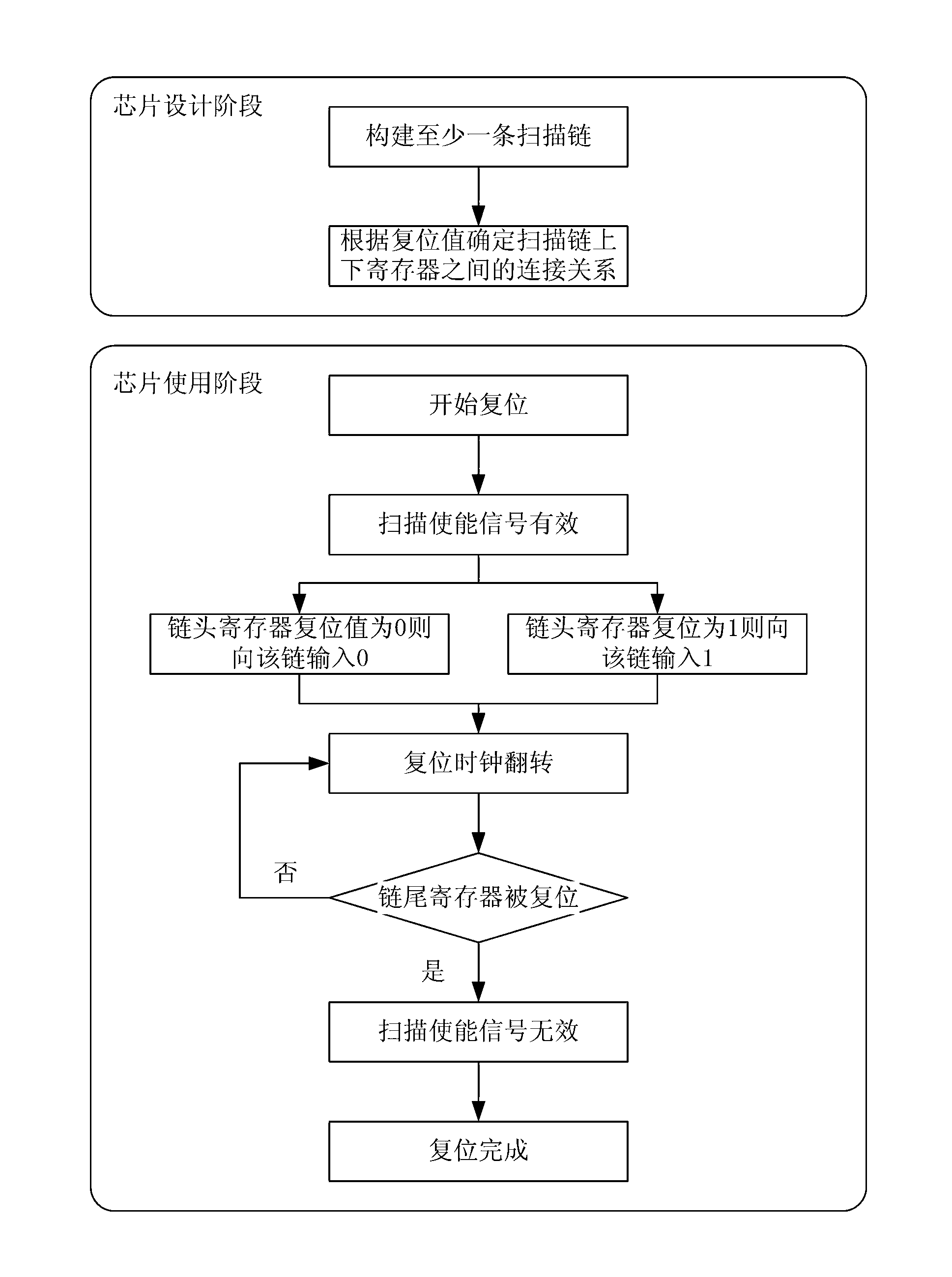

[0019] Such as figure 1 As shown, the implementation steps of the method for resetting the chip internal registers based on the scan chain in this embodiment are as follows:

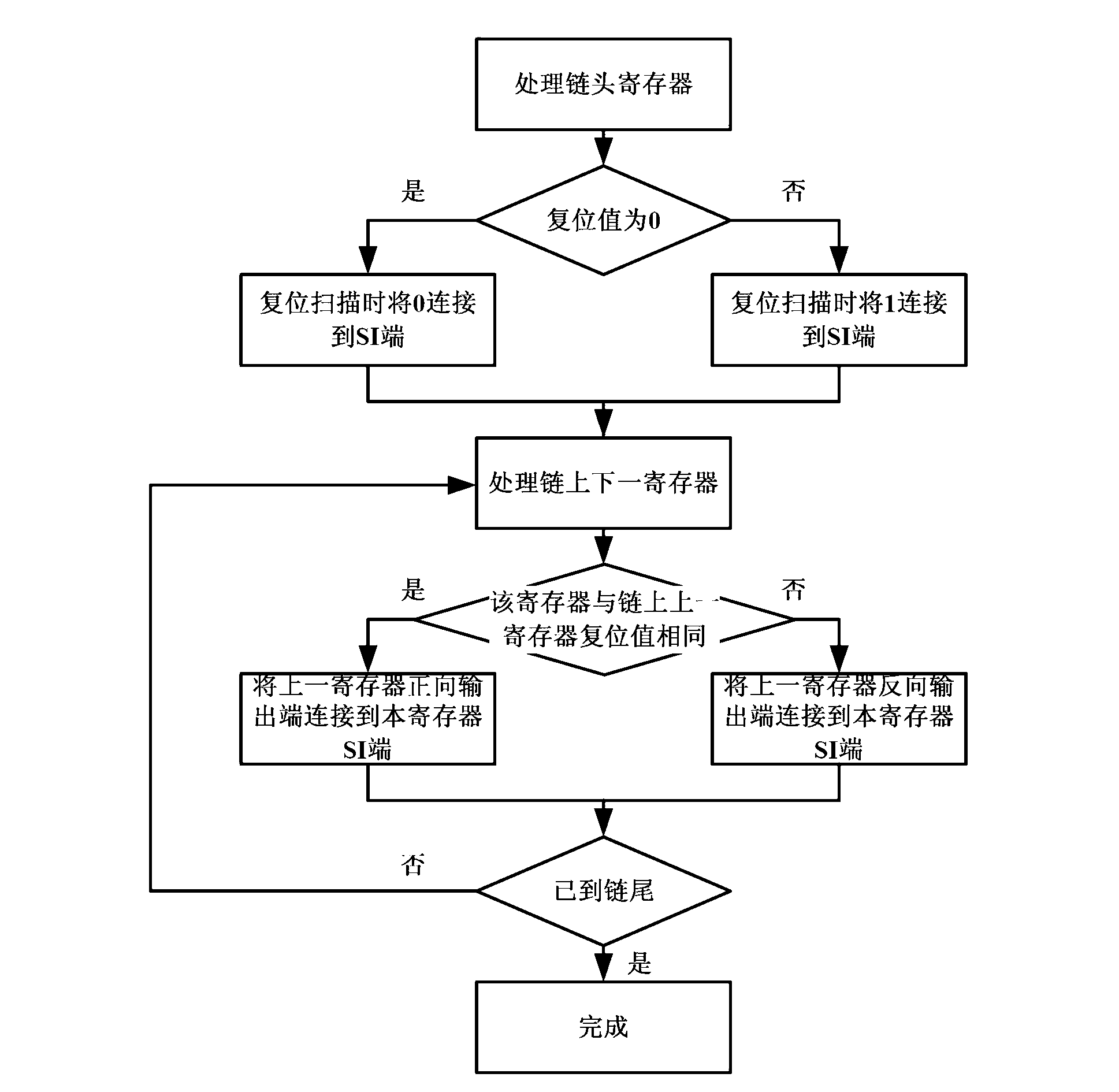

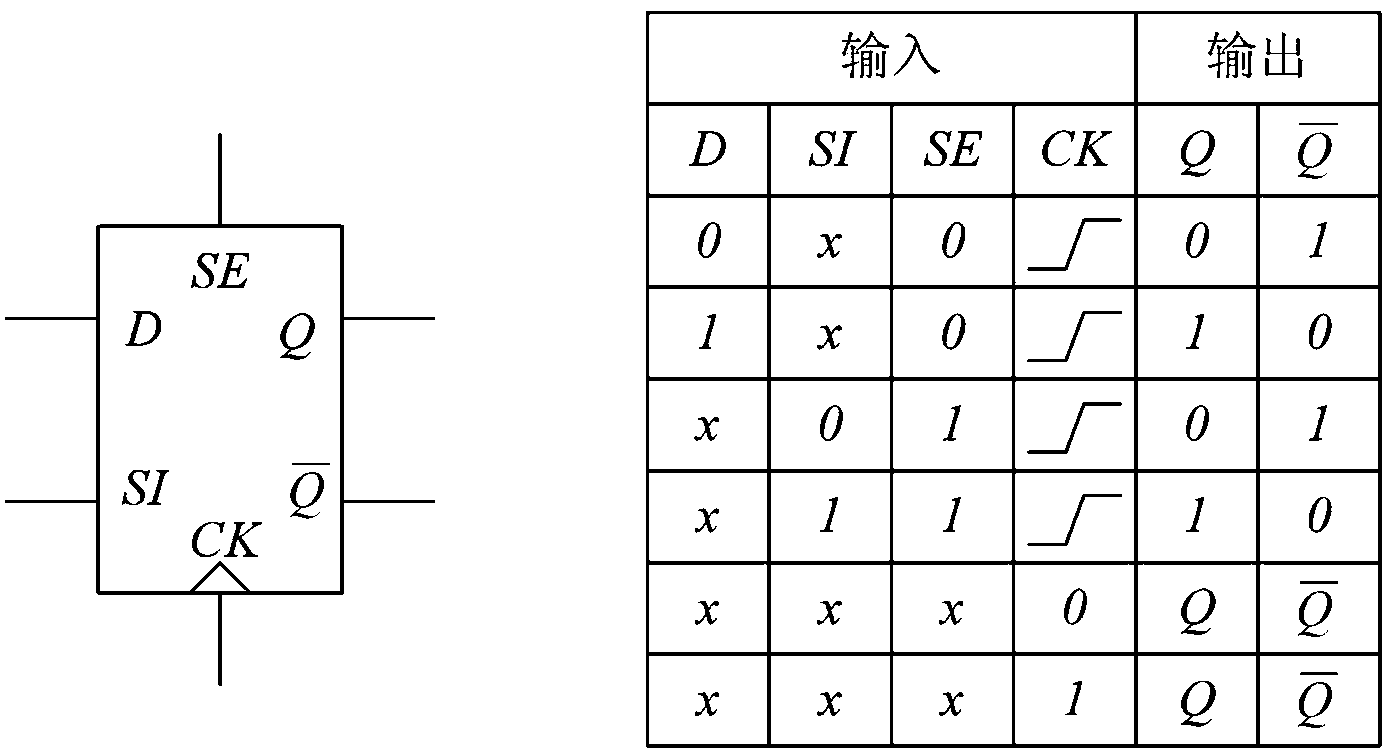

[0020] 1) In the chip design stage, the chain of registers that need to be reset is constructed as at least one scan chain, and when constructing the scan chain, the register and the previous scan chain are determined according to the reset value of the scan chain head register and the reset value of each register. The connection relationship between registers; if the reset value of the scan chain head register is 1, connect 1 to the scan input of the register; if the reset value of the scan chain head register is 0, connect 0 to the register If the reset value of the register is the same as that of the previous register in the scan chain, connect the scan input of the register to the positive output of the previous register in the scan chain; if the register is the same as the previous register in the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com