Multi-core multi-thread microprocessor-oriented virtual active page buffer method and device

A microprocessor and multi-threaded technology, applied in machine execution devices, electrical digital data processing, instruments, etc., can solve problems such as frequent opening and closing of active pages, frequent physical active pages, limited optimization space, etc., and achieve breakthrough access Memory bandwidth, multi-body load balance, and strong scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

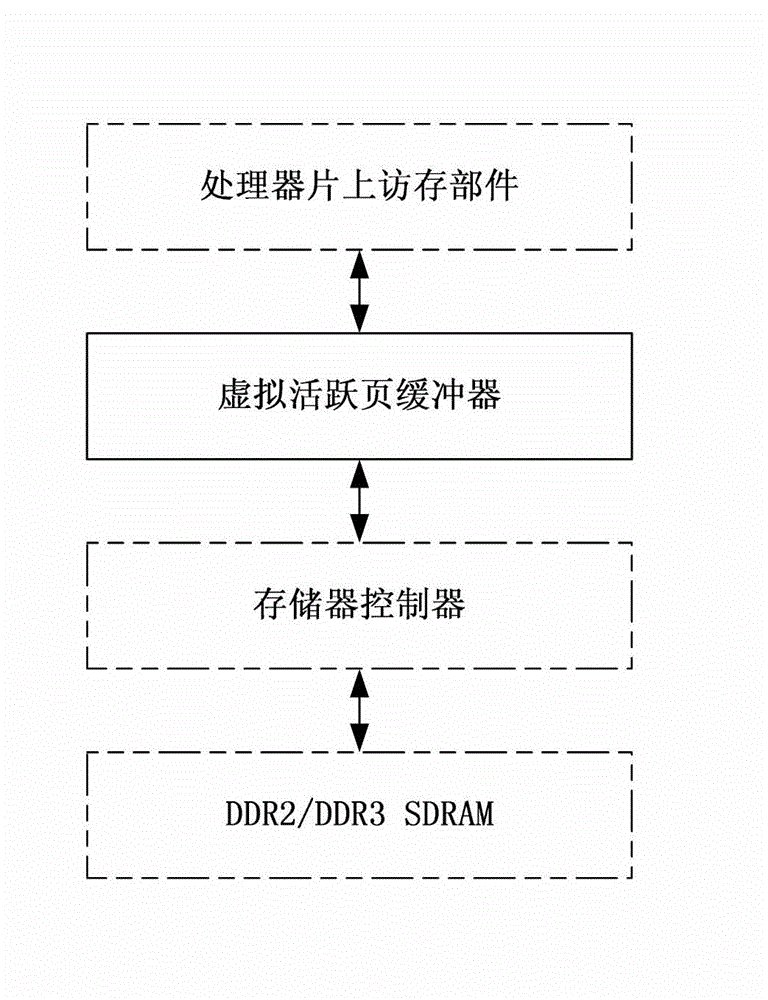

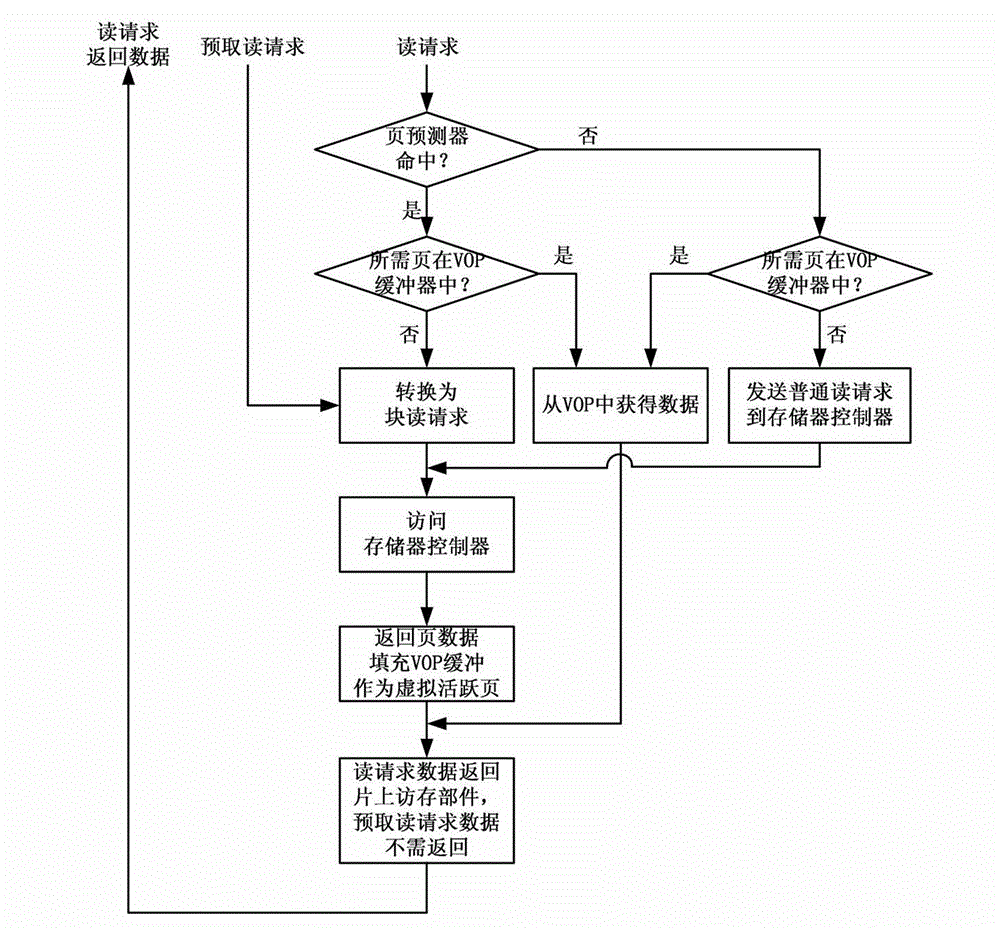

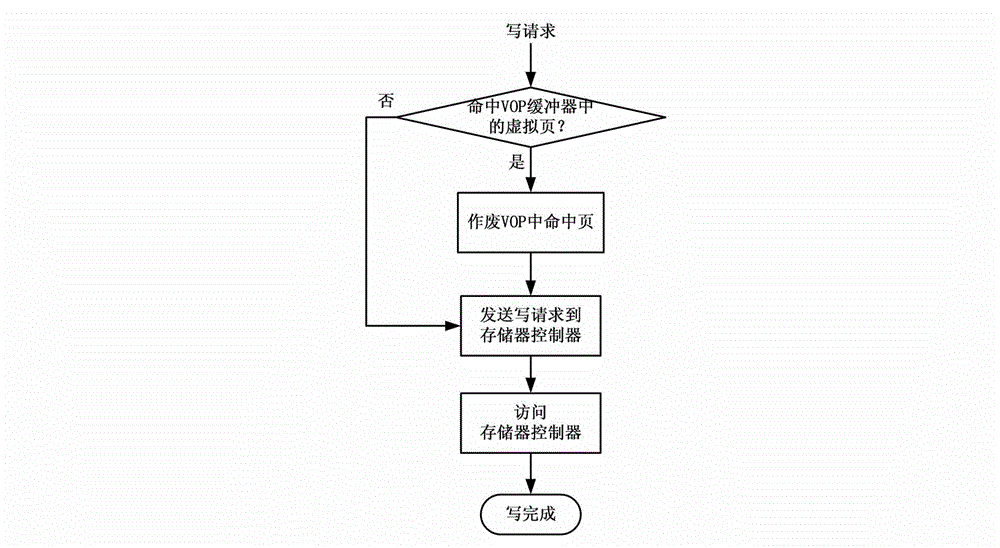

[0042] Such as figure 1 , figure 2 and image 3 As shown, the implementation steps of the virtual active page buffer method for multi-core multi-threaded microprocessors in this embodiment are as follows:

[0043] 1) Build a virtual active page buffer (Virtual Open Page Buffer, referred to as VOP buffer) between the on-chip memory access part of the processor and the memory controller, obtain the memory access request from the on-chip memory access part of the processor and judge the access The type of storage request, if the storage request is a read request, then jump to step 2); if the storage request is a prefetch read request, then jump to step 4); if the storage request is a write request, then jump Execute step 7);

[0044] 2) According to the request address of the memory access request and the request address of the historical memory access request, it is judged whether the memory access mode of the memory access request conforms to the preset rule access characte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com