Preparation method of SOI (silicon on insulator)-based SiGe-HBT (heterojunction bipolar transistor)

A transistor and base technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of lowering the maximum cut-off frequency Ft parameter, small vertical width of the collector region, and increased collector resistance of SiGe-HBT devices, etc. problem, to achieve the effect of easy implementation, avoiding the increase of doping concentration, and simple preparation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

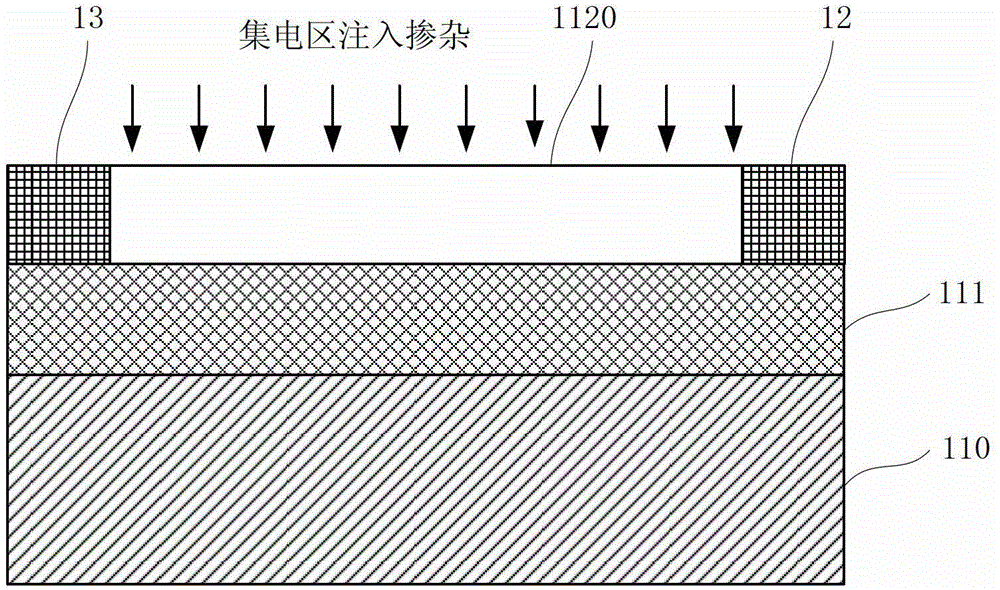

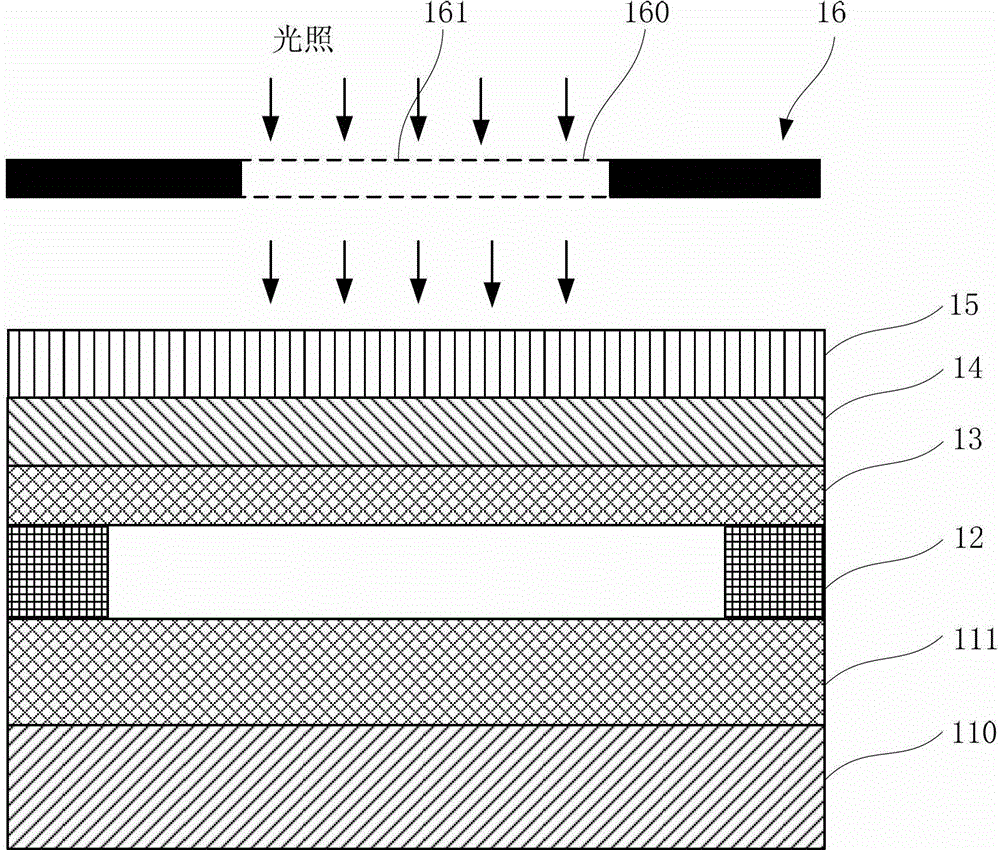

[0051] control attached Figure 1a to Figure 1m , the present invention provides a method for preparing an SOI-based vertical SiGe-HBT, comprising the following steps:

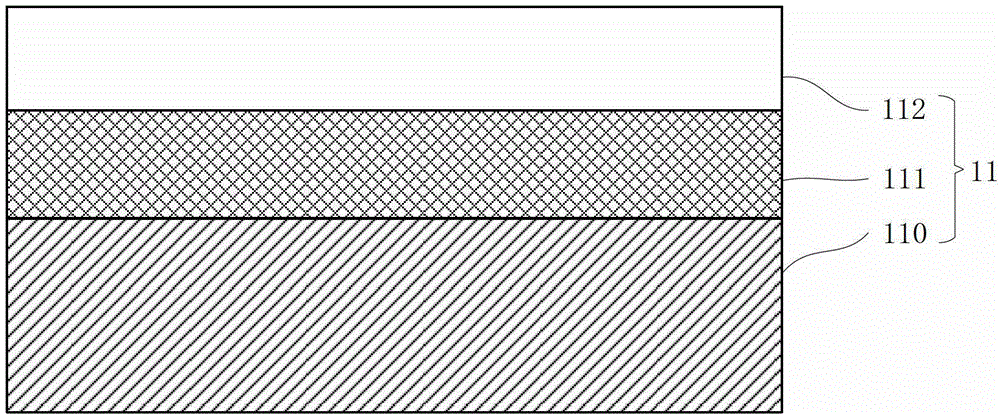

[0052] Step 1: If Figure 1a to Figure 1b As shown, an SOI substrate 11 is provided, including a back substrate silicon 110, a buried layer silicon oxide 111 and a top layer silicon 112, wherein the SOI substrate 11 is a conventional SOI starting wafer, and the thickness of the buried layer silicon oxide 111 is 100nm-200nm, the thickness of the top layer silicon 112 is 50nm-150nm. In this embodiment, the thickness of the buried layer silicon oxide 111 is temporarily selected as 150 nm, and the thickness of the top layer silicon 112 is temporarily selected as 100 nm, but it is not limited thereto. In other embodiments, other thicknesses can also be used, such as the buried layer The thickness of the silicon oxide 111 may be 100nm, 120nm, 180nm, or 200nm, etc., and the thickness of the top layer silicon 112 ma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com