Method for extracting and calculating capacitance parameter based on random walk in integrated circuit design

An integrated circuit and parameter extraction technology, which is applied in calculation, electrical digital data processing, special data processing applications, etc., can solve the problems of no further optimization of weight, slow calculation rate, and large memory consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

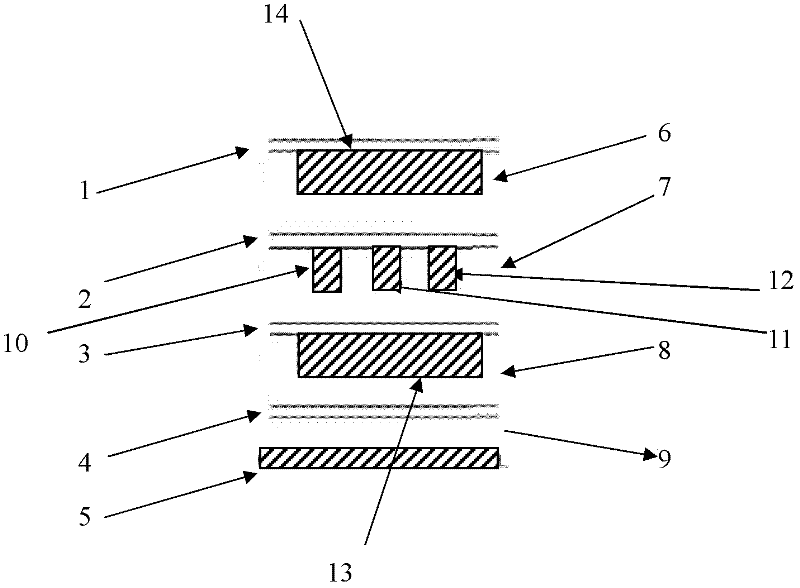

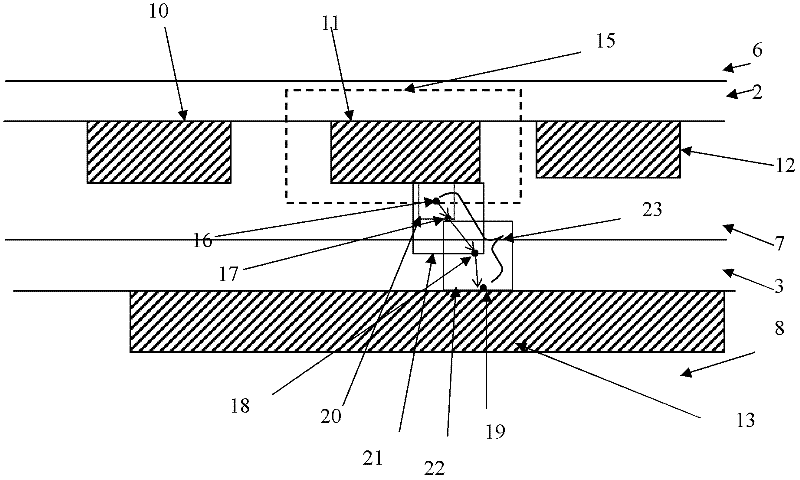

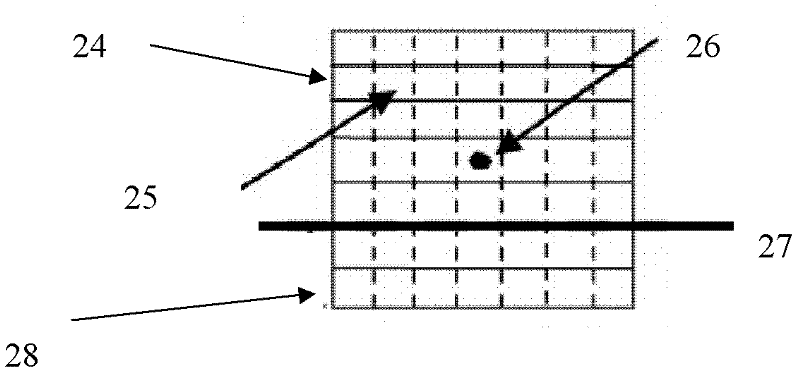

[0056] The database building and importance sampling processing of the present invention have been realized by MATLAB programming, and the FRW has been realized by C++ language programming, which can run on the LINUX operating system on the Intel workstation and the Linux operating system on the PC. Below in conjunction with a specific embodiment, the capacitance extraction process containing the importance sampling library construction process method is illustrated, so as to figure 1 For implementing an example, respectively place a long wire at the place of the long wire 10,11,12, respectively place 19 short wires at the place of the long wire 13 and 14, and intersect with the direction of the long wire 10,11,12 in a horizontal plane.

[0057] (1) Set the dielectric constant combination of the interface between two adjacent dielectric layers in the integrated circuit as (ε - =2.6,ε + =5), n=5 (in order to facilitate layout writing, set n=5 to be known, in order to ensure a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com