Parallel write-in multi-FIFO (first in,first out) implementation method based on single chip block RAM (random access memory)

An implementation method, a single-chip technology, applied in the field of information technology applications, can solve problems such as low resource utilization, insufficient number of memories, waste, etc., to achieve full utilization, enhance market competitiveness, and improve utilization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be further described below with reference to the drawings and embodiments.

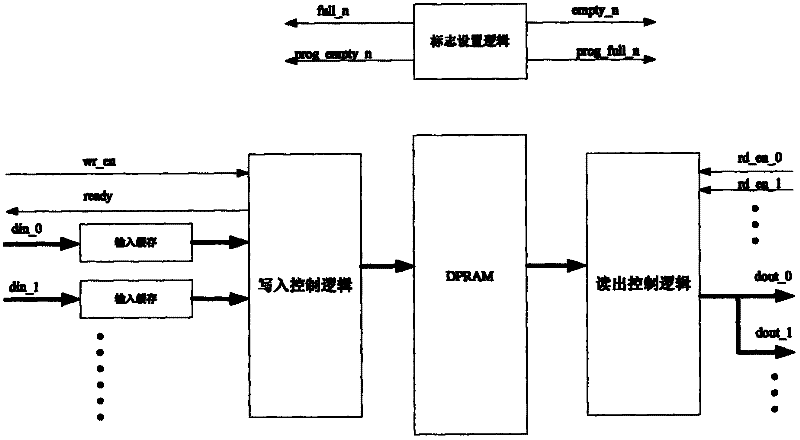

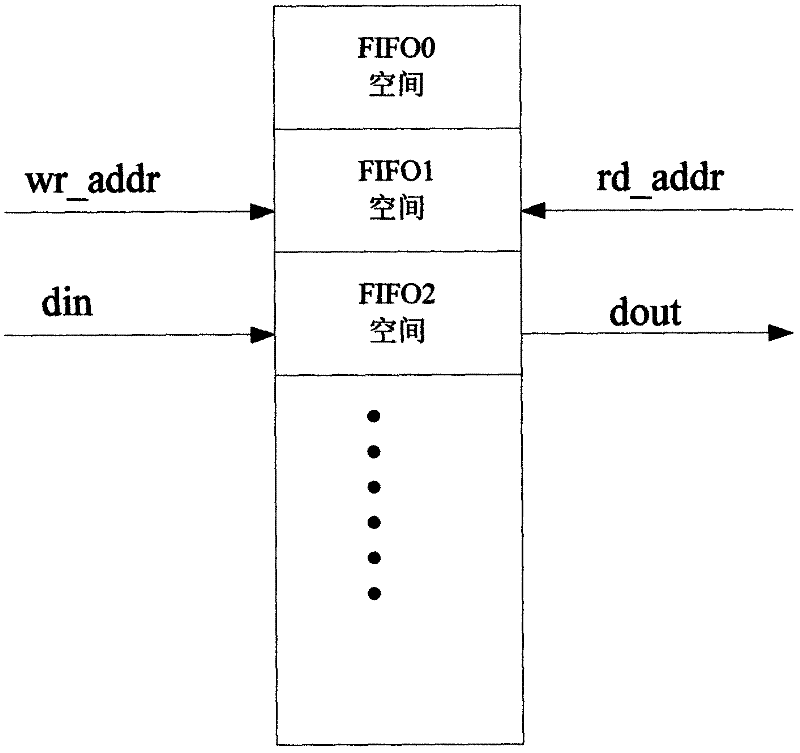

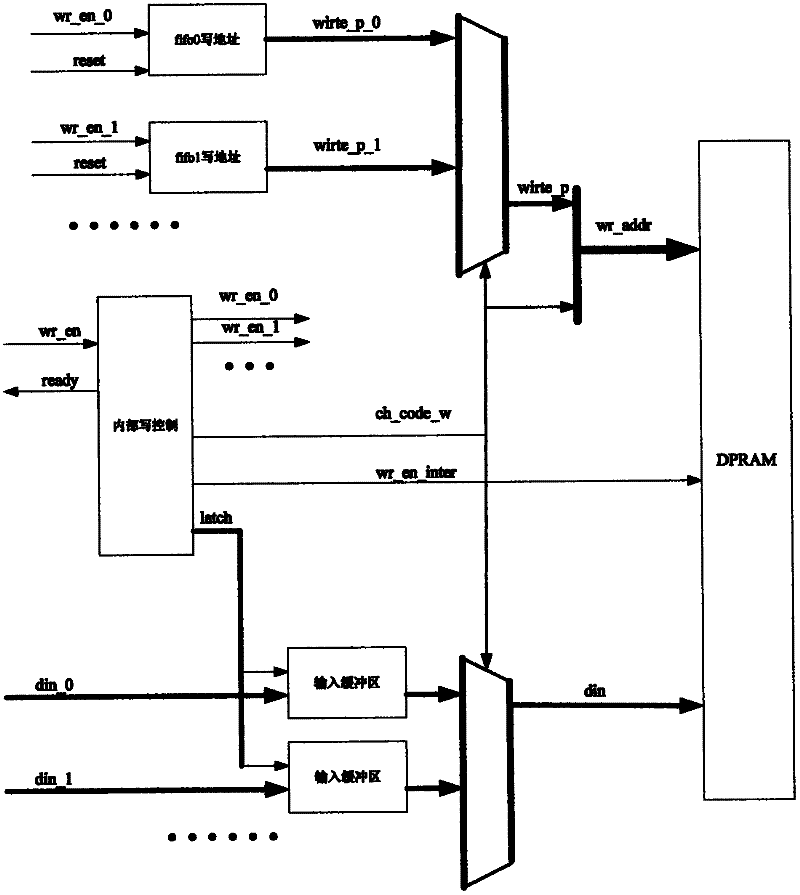

[0052] The present invention proposes a method for realizing multiple FIFOs that require parallel writing and random sequential readout by using a single block RAM. In this method, first use the IP core instantiation tool of the FPGA development platform to instantiate the block RAM into a DPRAM for storing the FIFO data of each channel; the write control logic can accept parallel FIFO data write requirements of each channel, and write the control logic After receiving the external write signal, the data is stored in the corresponding buffer of each channel FIFO, and then the internal write command is generated, and the data of each buffer is written into the storage space corresponding to the DPRAM in turn; when the external read request is received, The read control logic will read the data from the storage space corresponding to the DPRAM according to the requirements...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com