Method for reducing transient power consumption

A transient power consumption and clock technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as damage, failure to work, and functional errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] specific implementation plan

[0028] The technical solutions proposed by the present invention will be described in detail below in conjunction with the accompanying drawings.

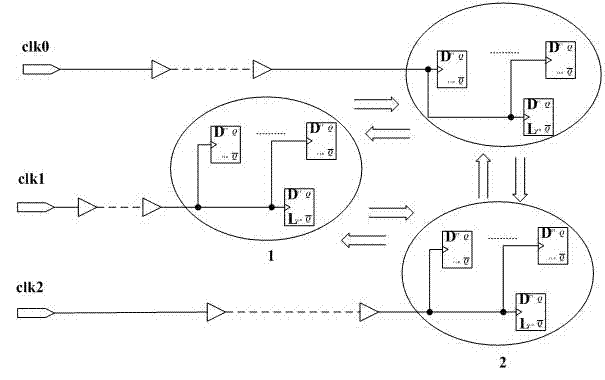

[0029] Such as figure 1 As shown in , it is assumed that there are 3 clock domains in the circuit design, namely clk0, clk1 and clk2, and there is a fixed phase relationship between clk1 and clk2.

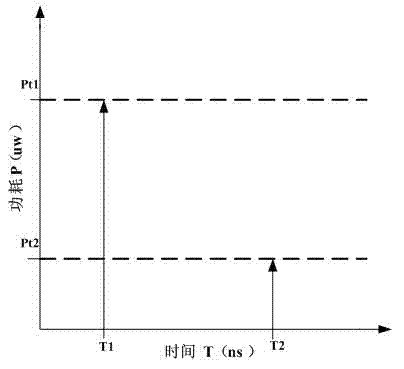

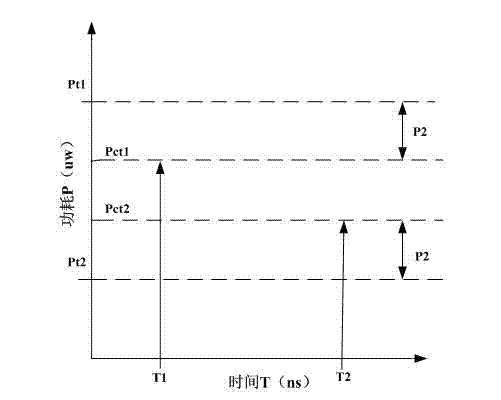

[0030] Assuming that the CP delay of clk1 is Dclk1, and the CP delay of clk2 is Dclk2, when the phase difference between Dclk1, Dclk2 and the two clock domains is 0, the registers in circuit combinations 1 and 2 with the same characteristics will be at time T1 At the same time, it is assumed that the power consumption required for the flipping of all registers in circuit combination 1 is P1, the power consumption required for flipping all registers in circuit combination 2 is P2, and the power consumption of all circuits except the registers of circuit combination 1 and 2 is Po1, then the total po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com