Failure message integrated device based on FPGA and ARM hardware platform

A fault information and fault technology, applied in the direction of fault location, etc., can solve the problems of no technical solutions, public reports, etc., and achieve the effect of small size, convenient use, and strong practicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] see figure 1 , including PT / CT board, ARM board, network switch board, serial port board, GPS board in the present embodiment, and the high-speed acquisition board that is made up of A / D sampling chip and FPGA. In order to match the pre-op amplifier, PT and CT require a maximum output of ±10V. The A / D chip selects ADS8556, which samples three voltages and three currents, and the sampling rate is 800K. The ADS8556 chip comes with a sample and hold circuit, uses external reference voltage, external clock, low power consumption, low noise, and three-state output.

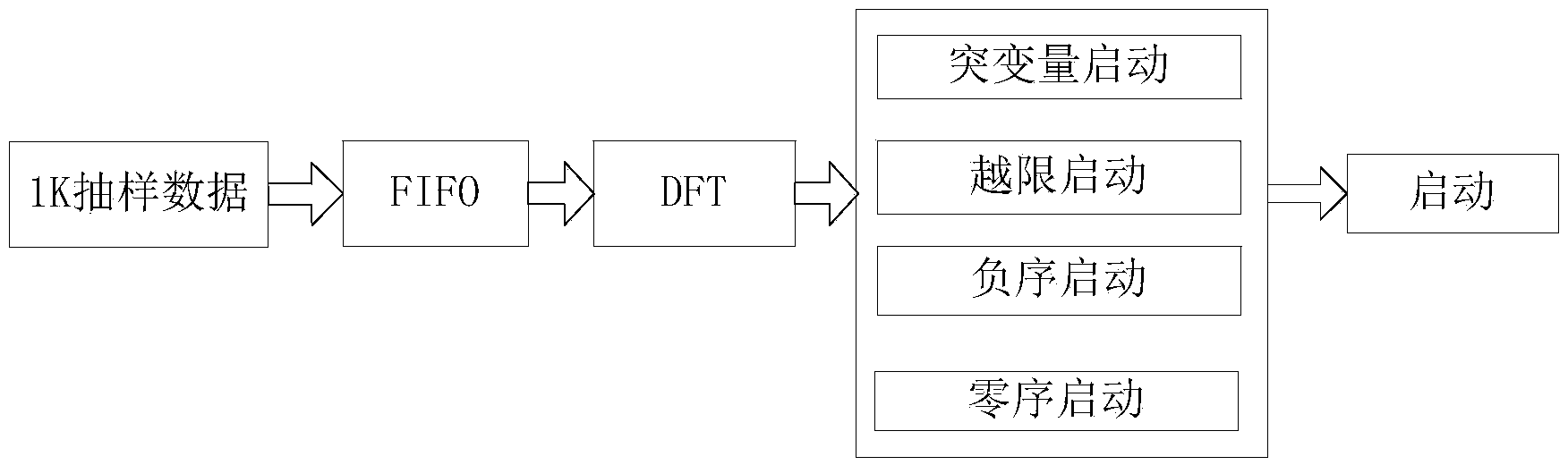

[0026] see figure 2 , under the control of FPGA, the AD sampling chip in the high-speed acquisition board collects the secondary side voltage and current signals from the PT / CT board, and obtains sampling data at a frequency of 800KHz. The 800KHz sampling data, on the one hand, is cyclically stored in the designated memory space in DDR2 through the DDR2 controller, as the recording data of the traveling wave ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com