High-threshold voltage gallium nitride (GaN) enhancement metal oxide semiconductor heterostructure field effect transistor (MOSHFET) device and manufacturing method

A high-threshold-voltage, enhancement-mode technology, used in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve problems such as lattice damage and low threshold voltage, reduce on-resistance, increase current density, The effect of improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

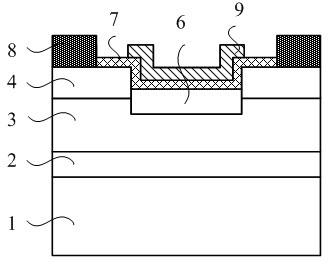

[0032] This example figure 1 A GaN high threshold voltage enhanced MOSFET device is given, including a substrate 1 and an epitaxial layer grown on the substrate 1, wherein the epitaxial layer includes a stress buffer layer 2, a GaN layer 3 and a heterogeneous layer from bottom to top. Structure barrier layer 4, etch heterostructure barrier layer 4 to GaN layer 3 in the gate area to form a groove, and selectively grow p-type GaN layer 6 on the groove, p-type GaN layer 6 and heterostructure An insulating dielectric layer 7 is deposited on the surface of the barrier layer 4, the insulating dielectric layer is etched on the source and drain regions of the heterostructure barrier layer 4, the gate metal 9 is evaporated on the gate region, and the source and drain regions are evaporated Plated ohmic contact metal8.

[0033] The heterostructure barrier layer 4 is one or any combination of AlGaN, AlInN, AlInGaN, and AlN materials, and the heterostructure barrier layer is an undoped l...

Embodiment 2

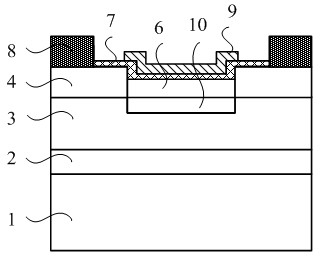

[0048] Such as figure 2 As shown, this embodiment provides a second structure of a GaN enhancement type MOSHFET device, which is roughly the same as the device structure of Embodiment 1. The difference is that the selective growth structure of the gate region is a double-layer epitaxial structure of u-GaN layer 10 and p-GaN layer 6 . The u-GaN layer can improve the crystal quality of the p-GaN layer and improve device performance.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com