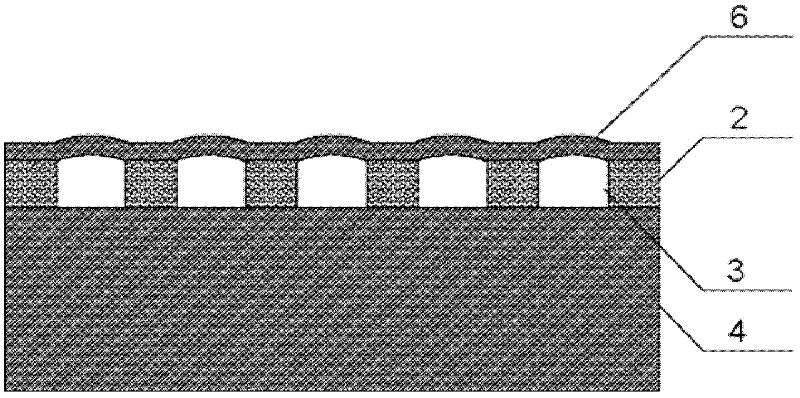

Process for reducing chemical-mechanical polishing crack on buried layer cavity silicon-on-insulator (SOI) wafer

A chemical-mechanical and hollow-type technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as easy deformation or even cracking of the top silicon film, poor consistency of top silicon film thickness, and product quality decline. Achieve the effect of reducing cracking, increasing yield and improving uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to better understand the process of the present invention, an example is given. The goal is to obtain an SOI wafer with a thickness of the top silicon film 7 of 5 μm and a bonding cavity 3 of 3 μm×3 μm×1 μm. The process flow is as follows: silicon wafer→oxidation→etching→calculation of pressure→bonding→thinning→polishing.

[0040] The semiconductor silicon substrate 4 provided by the present invention takes a P-type silicon wafer as an example, with a thickness of 300 μm and a diameter of 100 mm.

[0041] Step 1: Oxidize a silicon dioxide dielectric layer 2 with a thickness of 1000 nm on the surface of the silicon substrate 4 through a wet oxygen oxidation process. This process actually consumes about 475 nm in thickness of the silicon substrate 4 . The thickness of the silicon dioxide dielectric layer 2 can be used for subsequent formation of the bonding cavity 3 . The typical oxidation temperature is 1050°C, the oxidant is water vapor, and the oxidation t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com