A positive high voltage level conversion circuit

A technology of voltage conversion circuit and conversion circuit, which is applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., which can solve the problems of increasing process cost, increasing NMOS transistors, and reducing conduction capacity. , to achieve the effect of enhanced driving capability, simple circuit structure and fast switching speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the accompanying drawings.

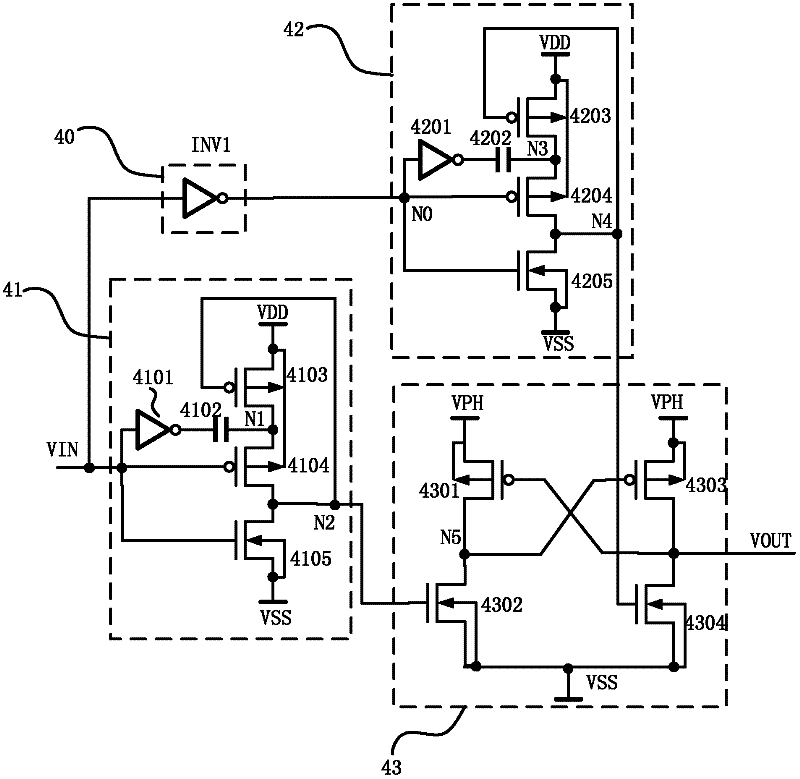

[0020] Such as image 3 As shown, the connection relationship of a positive high-voltage level conversion circuit is as follows: the VIN input voltage is connected to the common node of the INV1 inverter 40 and the first bootstrap circuit 41, and the INV1 inverter 40 is also connected to the second bootstrap circuit 42 , the voltage converting circuit 43 is respectively connected to the first bootstrap circuit 41, the second bootstrap circuit 42 and the VOUT output voltage.

[0021] The connection relationship of the first bootstrap circuit 41 is as follows: the VIN input voltage is respectively connected to the input terminal of the first inverter 4101, the gate of the second PMOS transistor 4104 and the gate of the first NMOS transistor 4105, and the first inverter 4101 It is connected in series with the first capacitor 4102, the N1 node is respectively connected to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com