A Thyristor Structure with Low Trigger Voltage and Low Parasitic Capacitance

A technology with parasitic capacitance and low voltage, applied in the field of thyristor structure, can solve the problems that the working voltage cannot be effectively protected and the trigger voltage is high, and achieve the effects of small parasitic capacitance, reduced turn-on voltage, and fast turn-on speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

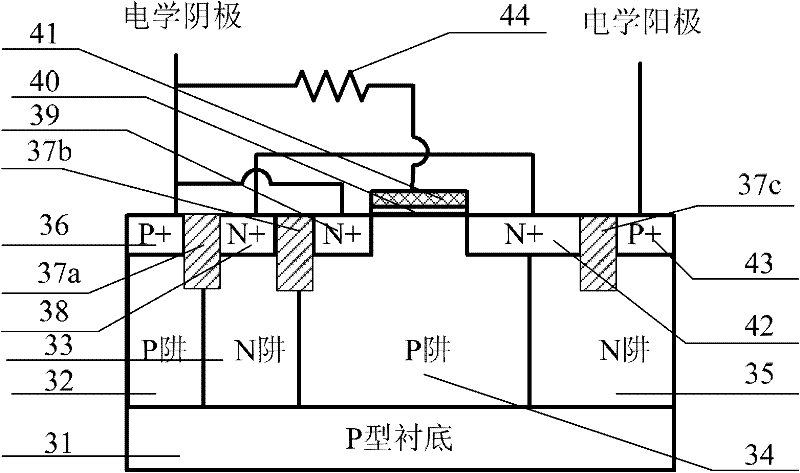

[0022] The present invention will be described in detail below in conjunction with the embodiments and accompanying drawings, but the present invention is not limited thereto.

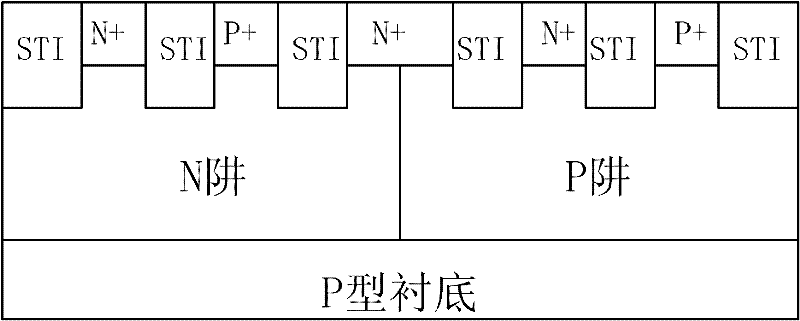

[0023] Such as image 3 As shown, a thyristor structure with low trigger voltage and low parasitic capacitance includes a P-type substrate 31, and a first P-well 32, a first N-well 33, and a second P-well 34 are sequentially arranged on the P-type substrate 31 and the second N well 35, wherein the first P well 32 is closely connected to the first N well 33, the first N well 33 is closely connected to the second P well 34, and the second P well 34 is closely connected to the second N well 35 ;

[0024] Wherein, on the direction from the first P well 32 to the second N well 35, on the first P well 32, the first N well 33, the second P well 34 and the second N well 35, there are arranged in sequence: the first P+ Implantation region 36, the first N+ implantation region 38, the second N+ implantation reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com