Multi-project wafer cutting method supporting constraint and limitation on positions of chips

A technology that supports chips and dicing methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as chip combination, difficulty in achieving mask area, and inability to minimize mask area, so as to achieve cost reduction Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

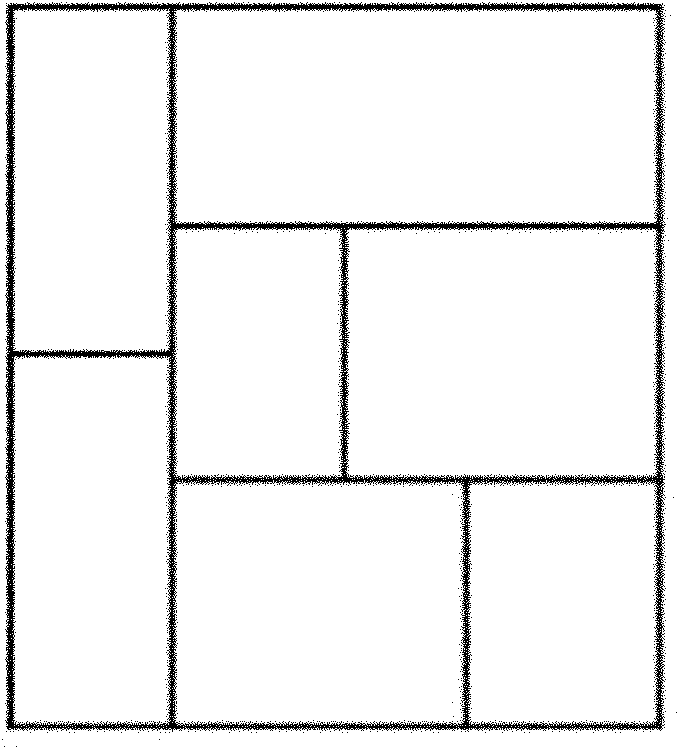

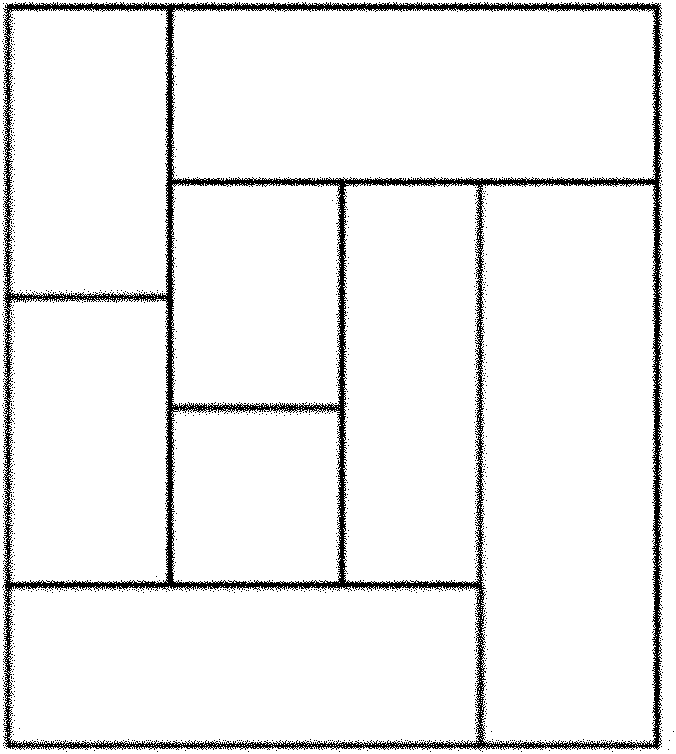

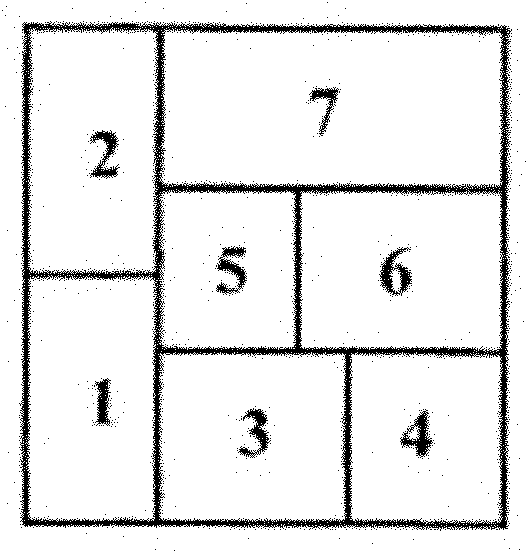

Image

Examples

Embodiment Construction

[0069] In order to describe the present invention more specifically, the multi-item wafer cutting method of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0070] Such as Figure 6As shown, the flow of a multi-item wafer dicing method that supports chip position constraints is as follows:

[0071] (1) Obtain information on the number, area and location of chips;

[0072] The position placement information includes the information of placing some chips at specific positions on the mask according to the actual production test requirements and the information of placing some chips with the same or similar shape and size at adjacent positions, and any of the two chips If the side lengths are equal, the two shapes are considered to be similar in size.

[0073] (2) According to the placement information of chips in step (1), the chips with the same or similar shape and size that need to be placed in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com