EEPROM erasing and writing method and device

A technology for writing devices and circuits, applied in information storage, static memory, instruments, etc., can solve the problems of increased power consumption, low breakdown voltage, large substrate leakage current, etc., to prevent the generation of negative voltage, reduce clamp Potential voltage, the effect of improving the breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

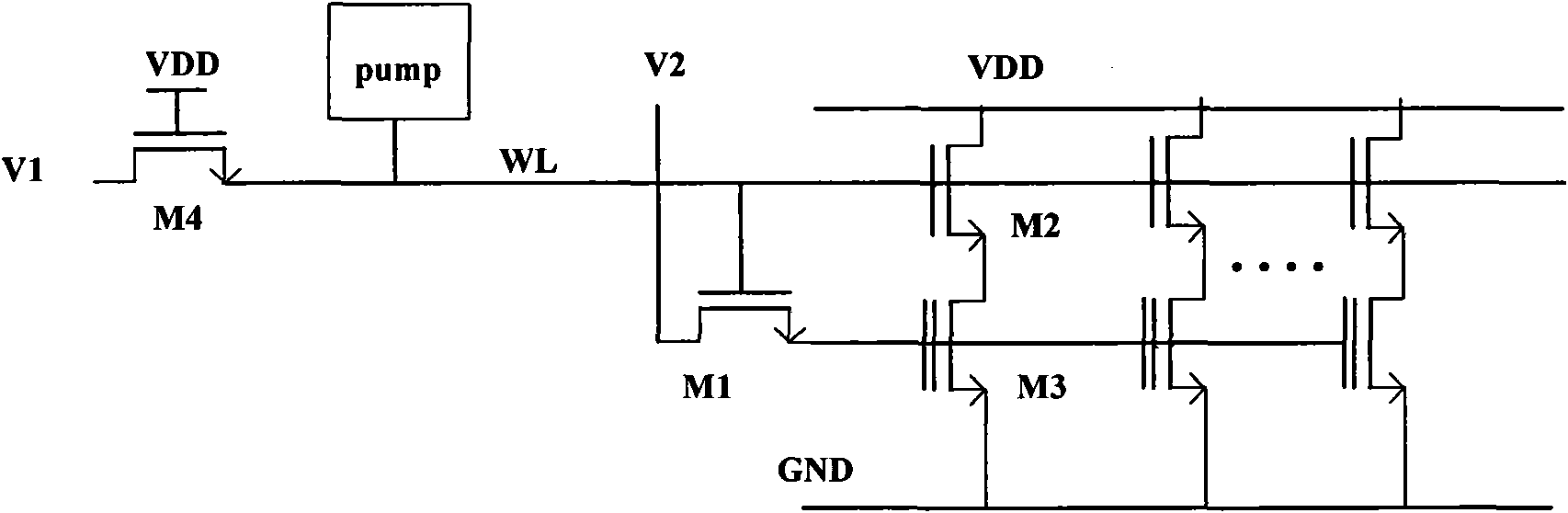

[0037] Image 6 It is a flow chart of the erasing and writing method of the EEPROM of the present invention. like Image 6 As shown, in step S1, the row selection signal V1 is used to control the charge pump circuit to realize row selection. In one embodiment of the present invention, a second logic signal can be used to control the clock signal of the charge pump circuit to be valid, and the second logic signal is a logic AND signal of the clock signal and the row selection signal V1. The clock signals include inverted non-overlapping clock signals, namely clock signal CLK and clock signal CLKB.

[0038] In step S2, a first logic signal is used to control the high-level row selection signal WL so that the high-level row selection signal WL has at least a voltage of logic 1 to increase the breakdown voltage, the first logic signal=write signal W+ Read signal R & row select signal V1.

[0039] In another preferred embodiment of the present invention, the power supply voltag...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com