Single event resistance latch structure based on state saving mechanism

An anti-single event, state preservation technology, applied in the direction of pulse generation, electrical components, reliability improvement and modification, etc., can solve the problems of increasing system timing overhead, achieve small area and power consumption, simple circuit structure, and reduce occupied area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described below in conjunction with specific drawings and embodiments.

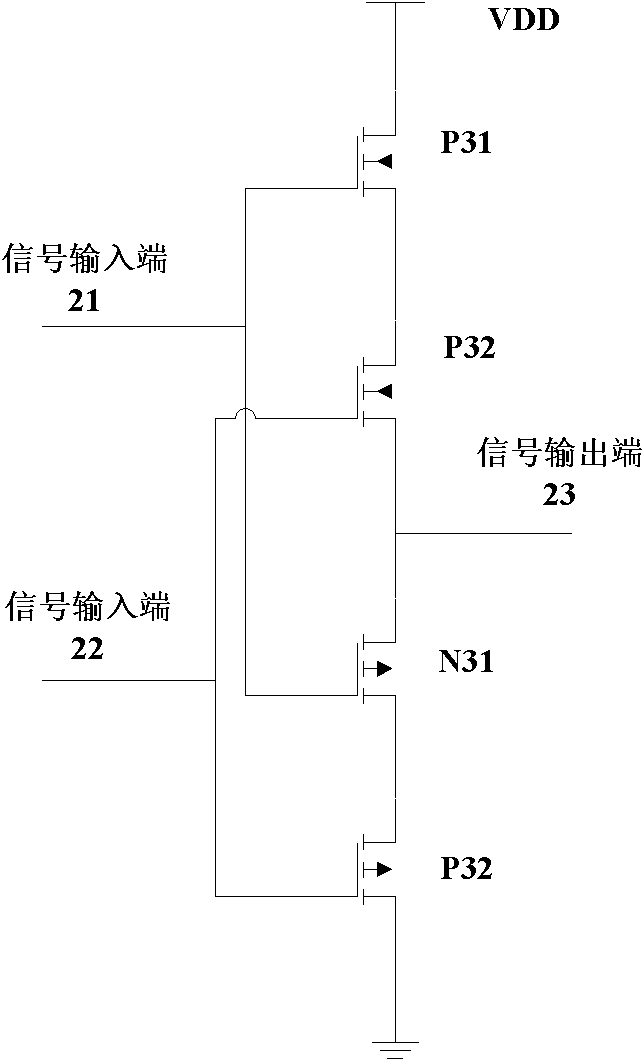

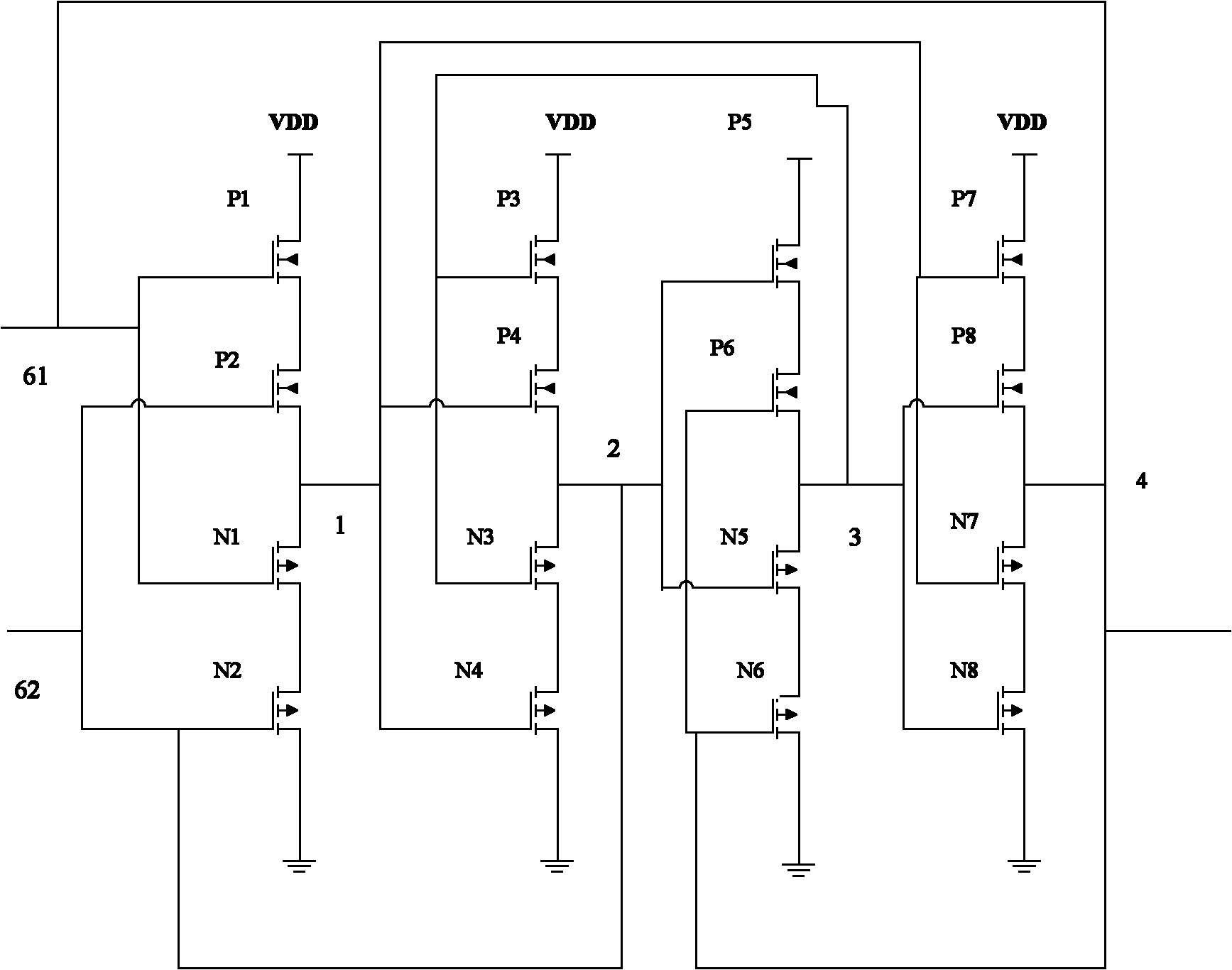

[0019] Such as Figure 1~Figure 4 As shown: the present invention includes a signal delay circuit, an anti-single event latch circuit, a first node 1, a second node 2, a third node 3, a fourth node 4, a control signal input terminal 5, a data input terminal 6, a data The output terminal 7 , the first latch circuit input terminal 61 and the second latch circuit input terminal 62 .

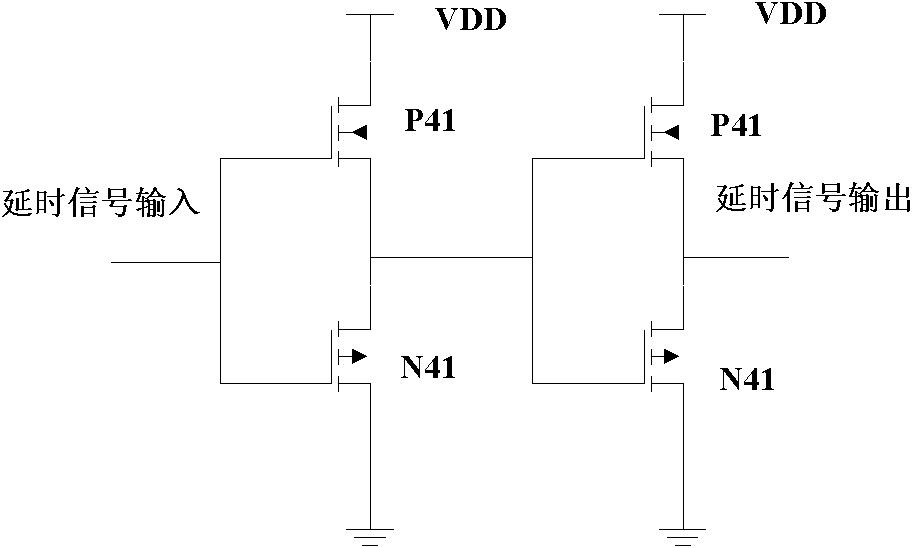

[0020] figure 1 Schematic diagram of the signal delay circuit. figure 1 In , only one set of inverter delay circuits in the signal delay circuit is shown. Such as figure 1 As shown: the inverter delay circuit includes two inverters; the inverter includes a MOS transistor P41 and a MOS transistor N41, the source terminal of the MOS transistor P41 is connected to the power supply VDD, and the drain terminal of the MOS transistor P41 is connected to the power supply VDD. The drain ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com