Method for etching interpoly dielectric

A polysilicon layer and dielectric technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as uneven thickness of the lower oxide layer, affecting the electrical thickness of the oxide layer, and damage to the silicon substrate, etc., to achieve etching The effect of stable rate, reduced damage and uniform thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the object, technical solution, and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

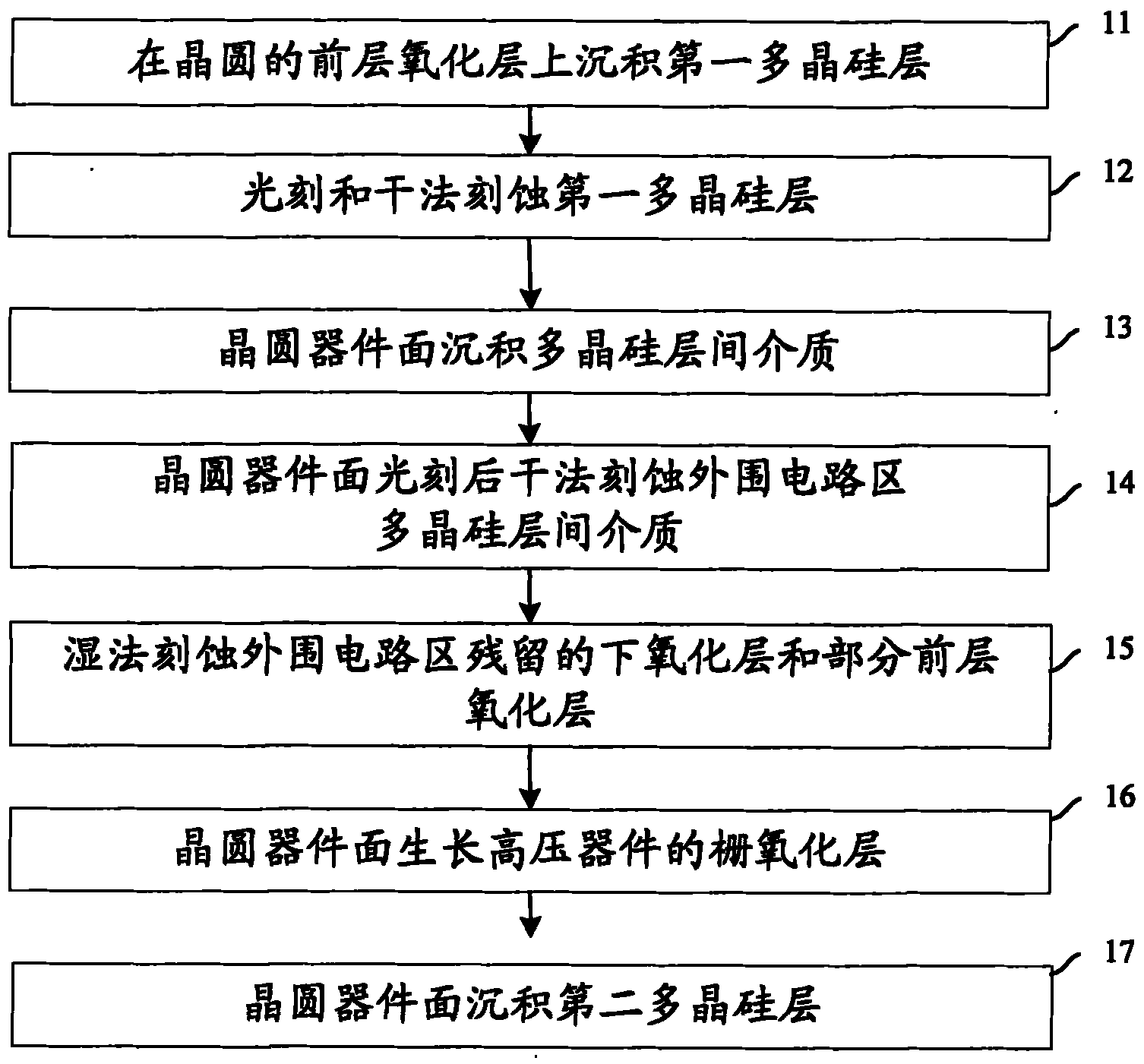

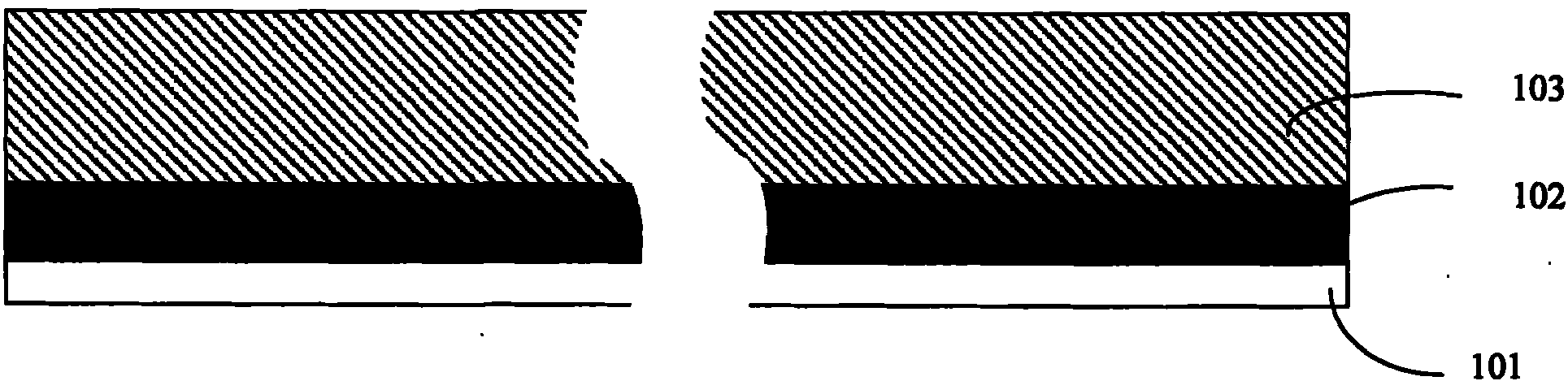

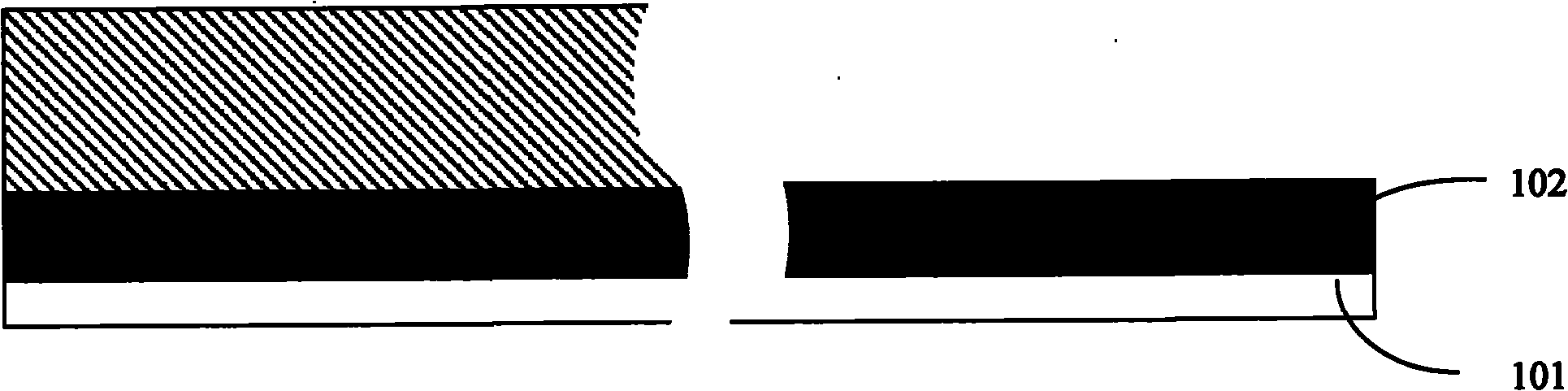

[0047] The specific process steps of polysilicon interlayer dielectric etching in the process of manufacturing the peripheral circuit area in the flash memory of the present invention are as follows: image 3 as shown, Figure 4a to Figure 4f It shows the cross-sectional diagram of the peripheral circuit area and the memory cell area in the etching process of the inter-polysilicon layer dielectric of the flash memory of the present invention:

[0048] Step 31, depositing the first polysilicon layer 103 on the front oxide layer 102 of the wafer 101, the peripheral circuit area and the memory cell area are obtained as follows Figure 4a The structure shown, wherein the right part represents the peripheral circuit area, and the left part represents the m...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com