Method for obtaining vertical channel high-voltage super junction-semiconductor device

A super junction and semiconductor technology, used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of high cost, complex process, poor stability and repeatability of mass production, etc., achieve high aspect ratio, reduce Effects of diffusion and low resistance resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

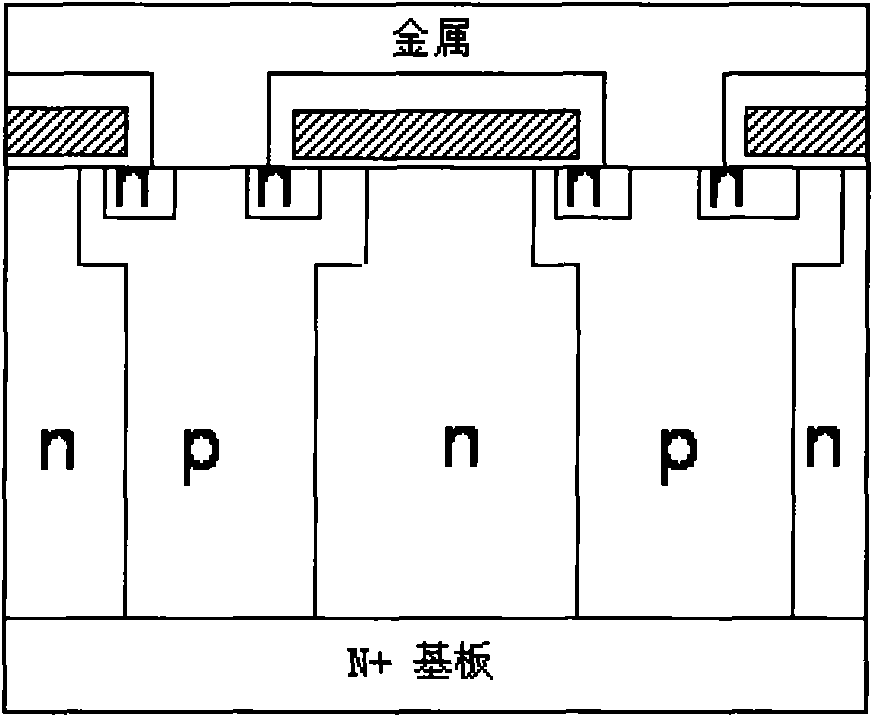

[0029] see Figure 2-8 As shown, the method for obtaining a vertical channel high-voltage super junction semiconductor device in the present invention includes the following process steps:

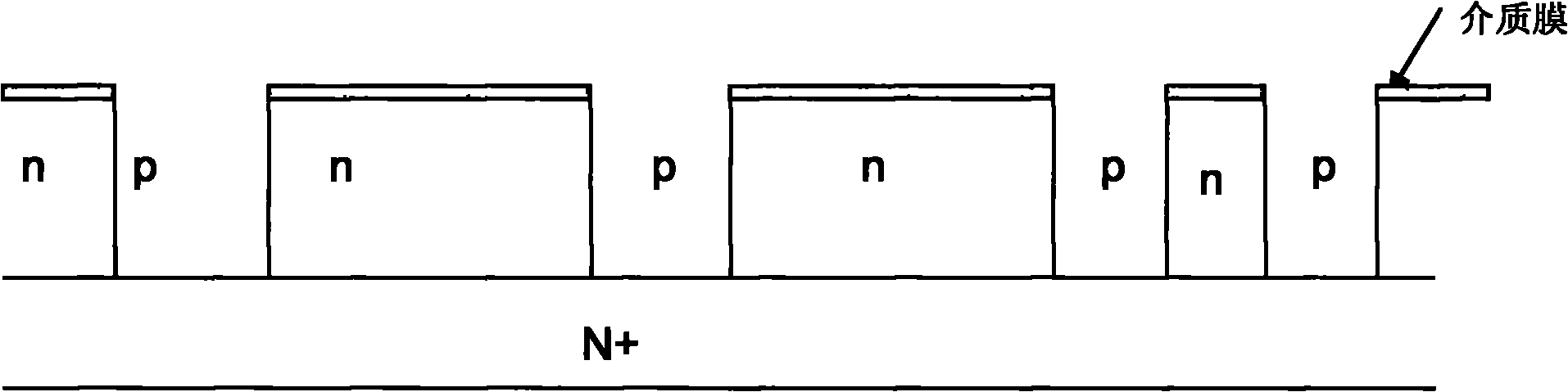

[0030] Step 1: Perform the first N-type epitaxial growth on the N+ substrate, and form a layer of dielectric film on the N-type epitaxial layer.

[0031] Step 2: Etching the N-type epitaxial layer, forming a groove with a certain aspect ratio on the N-type epitaxial layer to penetrate to the N+ substrate (see figure 2 shown). The etching method can adopt various known existing technologies. The trenches with a certain aspect ratio may be trenches with an aspect ratio greater than or equal to 4:1.

[0032] Step three, see image 3 As shown, the trench is filled with a P-type epitaxial layer.

[0033] Step 4, using chemical mechanical grinding to obtain a structure in which flat N-type pillars and P-type pillars appear alternately (combined Figure 4 shown).

[0034] Step 5. Perform ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com