On-chip control system of digital articulation based on FPGA (Field Programmable Gate Array)

A technology of control system and joint piece, which is applied in the field of robotics, can solve the problems of low integration of robot joint control system, and achieve the effect of high integration and short development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

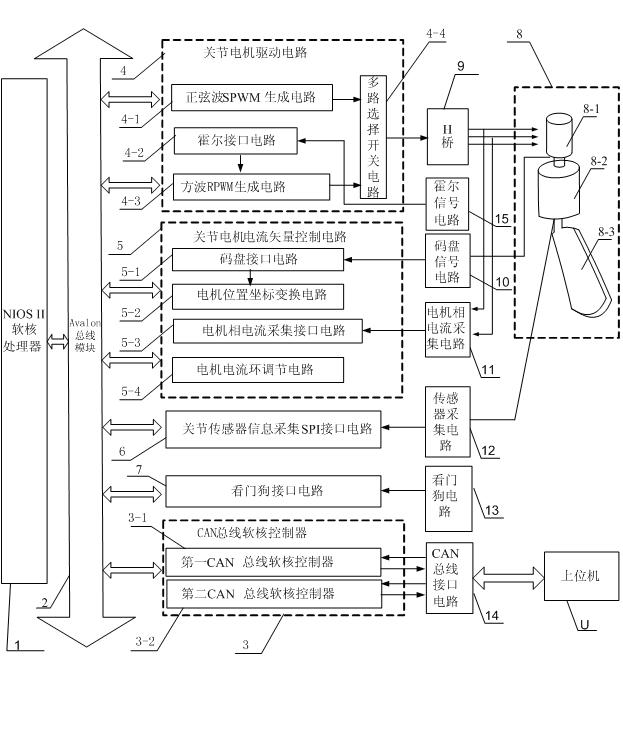

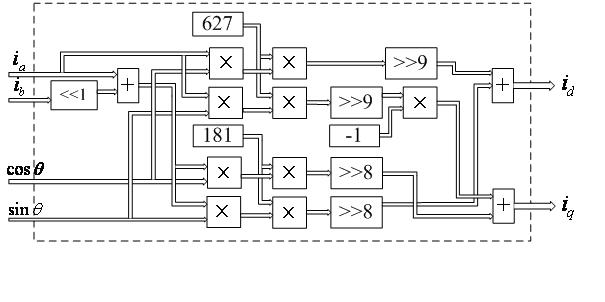

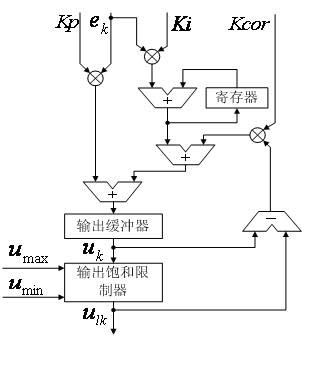

[0009] Specific implementation mode 1: According to the instructions attached figure 1 To specifically describe this embodiment, the FPGA-based digital joint on-chip control system described in this embodiment includes a NIOSII soft-core processor 1, an Avalon bus module 2, a CAN bus soft-core controller 3, a joint motor drive circuit 4, and a joint motor drive circuit 4. The motor current vector control circuit 5 and the joint sensor information acquisition SPI interface circuit 6, the CAN bus soft core controller 3 includes a first CAN bus soft core controller 3-1, and the joint motor drive circuit 4 includes a sine wave SPWM generation circuit 4-1 , the joint motor current vector control circuit 5 includes a code disc interface circuit 5-1, a motor position coordinate conversion circuit 5-2, a motor phase current acquisition interface circuit 5-3 and a motor current loop adjustment circuit 5-4; NIOSII soft core processor The communication end of 1 is respectively connected ...

specific Embodiment approach 2

[0011] Embodiment 2: The difference between this embodiment and Embodiment 1 is that the CAN bus soft core controller 3 further includes a second CAN bus soft core controller 3-2, and the second CAN bus soft core controls The communication end of the processor 3-2 is connected to the communication end of the NIOSII soft core processor 1 through the Avalon bus module 2.

[0012] In this specific implementation manner, a second CAN bus soft-core controller 3-2 is added to the FPGA, which realizes redundant CAN bus communication and improves the reliability of the communication system.

specific Embodiment approach 3

[0013] Embodiment 3: The difference between this embodiment and Embodiment 1 or 2 is that the FPGA-based digital joint system-on-chip further includes a watchdog interface circuit 7, and the watchdog interface circuit The communication end of 7 is connected to the communication end of the NIOSII soft core processor 1 through the Avalon bus module 2, and the watchdog interface circuit 7 is used to transmit a dog feeding signal or a dog bite signal.

[0014] In this specific embodiment, a watchdog interface circuit 7 is added to the FPGA, and the external watchdog circuit 13 can monitor the operation of the NIOSII soft-core processor 1 in the FPGA, prevent programs from running away, and improve the reliability of the system.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com