Time synchronization method, device and system of xDSL

A time synchronization and time technology, applied in the field of communication, can solve problems such as large line noise, affecting the accuracy of time synchronization, large errors, etc., and achieve the effect of time synchronization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be clearly and completely described below in conjunction with the accompanying drawings:

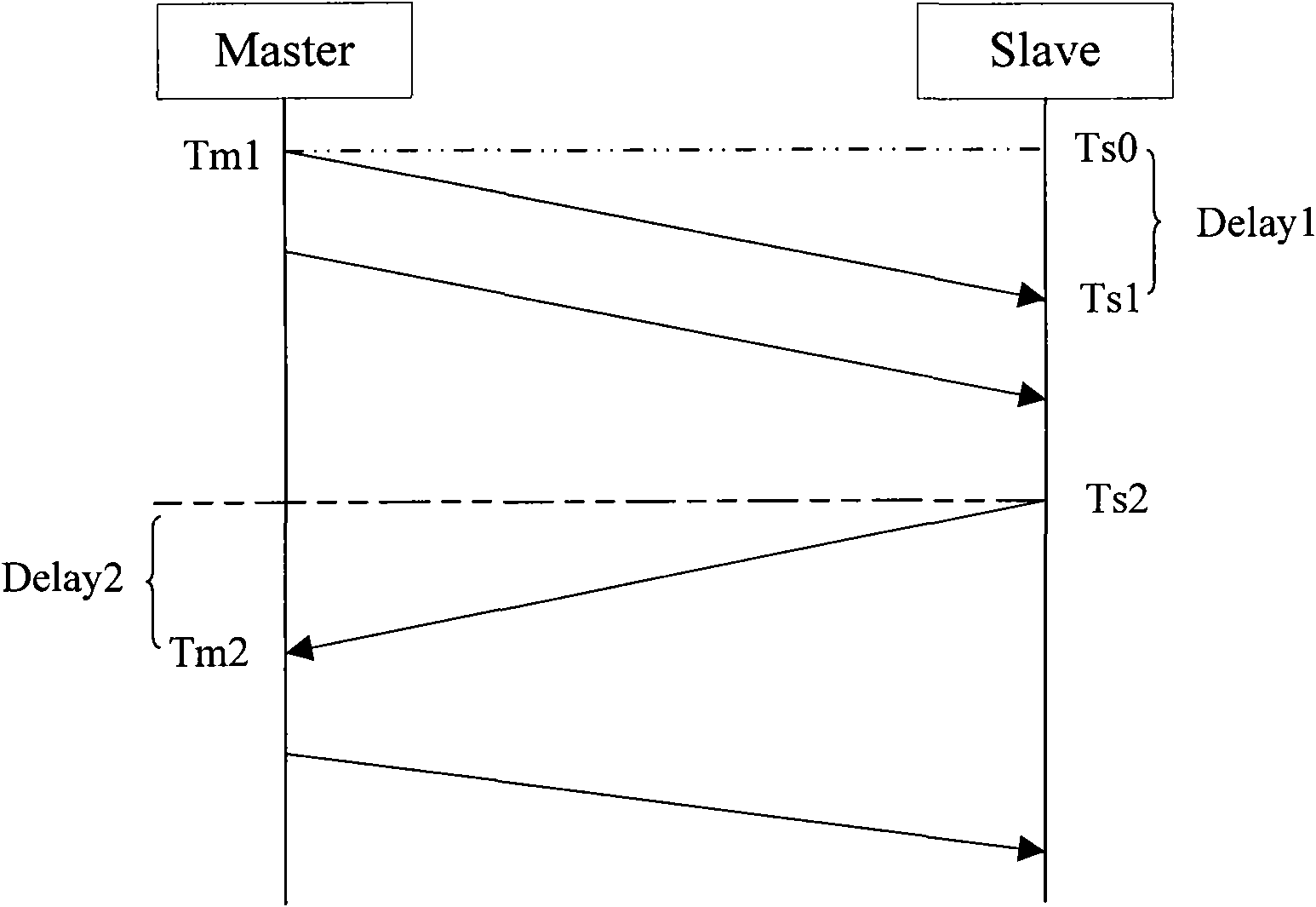

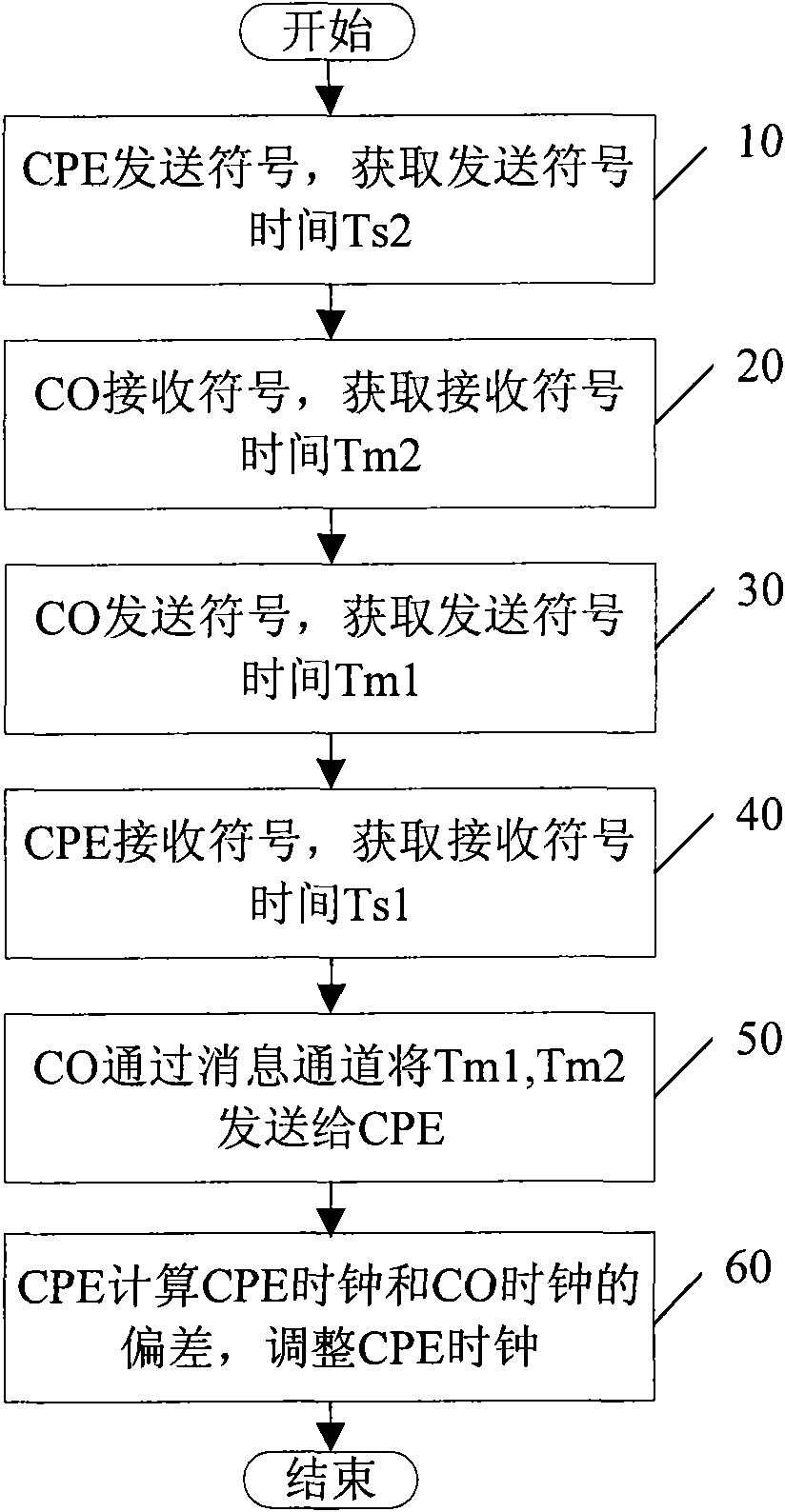

[0045] The first embodiment of the present invention provides an xDSL time synchronization method, including the following steps: the first device sends a first symbol to the second device, and obtains the time Ts2 for sending the first symbol;

[0046] The first device receives the second symbol sent by the second device, and acquires time Ts1 for receiving the second symbol;

[0047] The first device obtains the time Tm2 when the second device receives the first symbol and the time Tm1 when the second device sends the second symbol;

[0048] The first device calculates the deviation between the clock of the first device and the clock of the second device according to the Ts1, Ts2, Tm1, Tm2, and the delay of the first device;

[0049] The first device adjusts a clock of the first device according to the offset to achieve synchronization. In the foll...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com