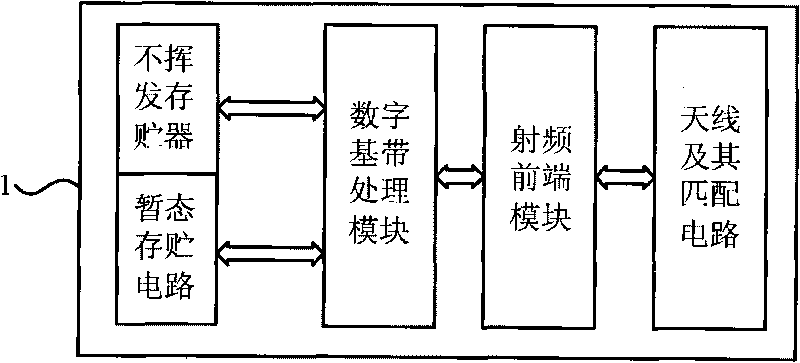

Transient storage circuit suitable for CMOS integration and using method thereof

A circuit and suitable technology, applied in the field of radio frequency identification, can solve problems such as the decline of identification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

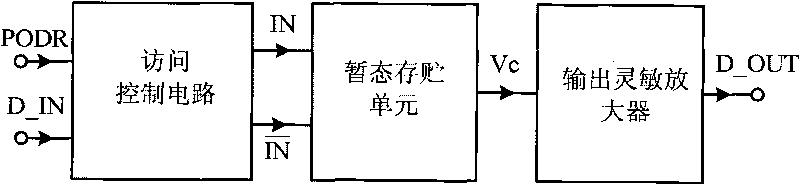

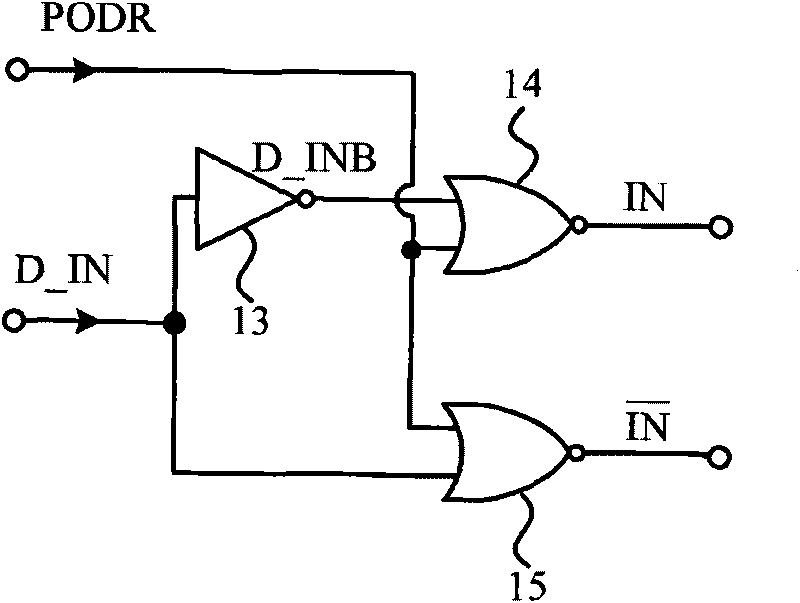

[0089] see Figure 2 to Figure 4 and Figure 10 to Figure 14 , The transient storage circuit of the present invention is composed of an access control circuit, a transient storage unit and an output sensitive amplifier connected in sequence. The reset signal PODR and the input data signal D_IN of the digital circuit of the tag chip are written into the transient storage unit through the access control circuit, and the temporary storage data output Vc of the transient storage unit is amplified by the output sensitive amplifier and then output by the data line D_OUT. According to the reset mode of the reset signal, the access control circuit is one of the following two structures:

[0090] 1) The reset signal PODR is valid for high level reset and digital system for normal operation at low level. The input data signal D_IN is respectively connected to one input terminal of NOR gate 2 15 and connected to NOR gate 1 14 via inverter 1 13 One input end of NOR gate 14 and the other...

Embodiment 2

[0112] see Figure 5 to Figure 14 , The transient storage circuit of the present invention is composed of an access control circuit, a transient storage unit and an output sensitive amplifier connected in sequence. The reset signal PODR, input data signal D_IN and write enable signal WEN of the digital circuit of the label chip are written into the transient storage unit through the access control circuit, and the temporary storage data output Vc of the transient storage unit is amplified by the output sensitive amplifier and then amplified by the data Line D_OUT output. According to the reset mode of the reset signal, the access control circuit is one of the following four structures:

[0113] 1) When the reset signal PODR is high, the reset is valid, and when the low level is low, the chip works normally. When the write enable signal WEN is low, it is valid to write to the transient storage circuit. When WEN is high, the transient storage circuit is in the data transient st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com