Vertical double diffused metal oxide semiconductor field effect transistor

An oxide semiconductor, vertical double diffusion technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of long terminal length and large chip area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

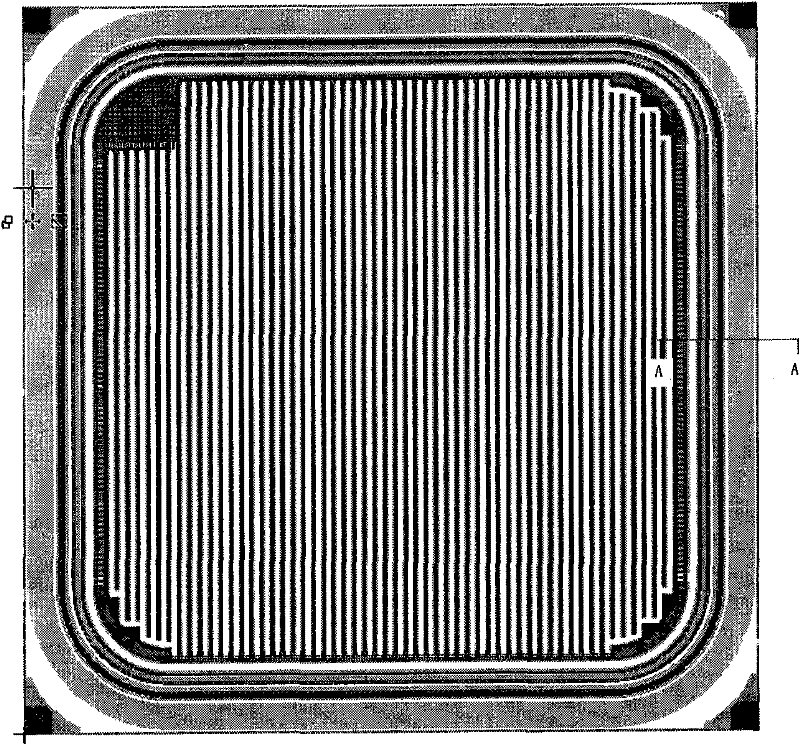

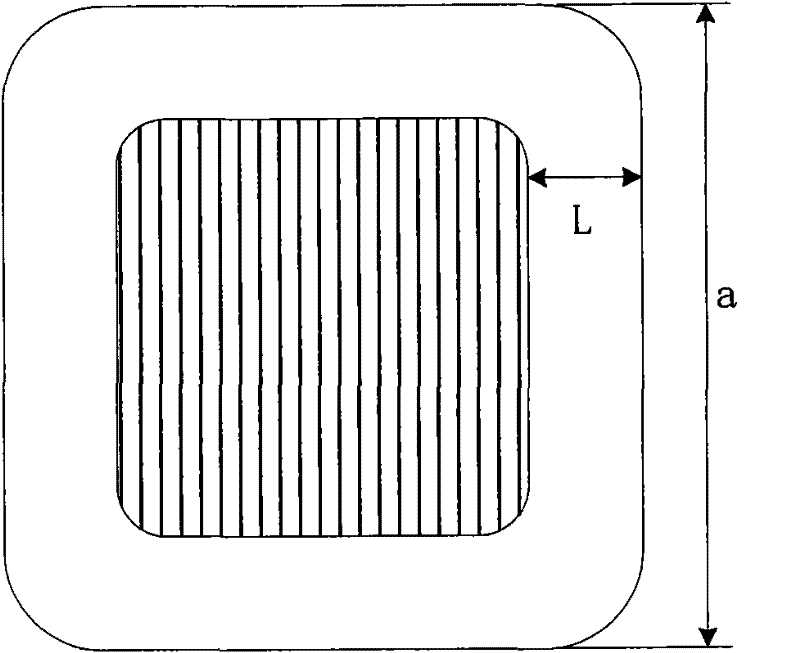

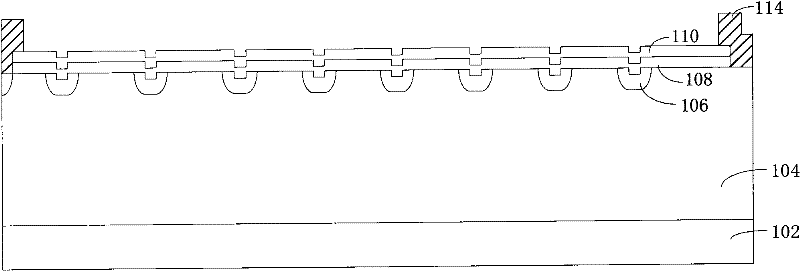

[0020] Figure 4 It is a cross-sectional view of the terminal structure of the first embodiment when the design withstand voltage of the vertical double-diffused metal oxide semiconductor field effect transistor is 650V. The first embodiment of the vertical double-diffused metal oxide semiconductor field effect transistor adopts an N-channel field effect transistor, including a silicon-based substrate 202, an epitaxial layer 204 on the silicon-based substrate 202, and a plurality of epitaxial layers arranged on the top of the epitaxial layer 204 The voltage divider ring 206, the oxide layer 208 on the epitaxial layer 204, the polysilicon field plate 210 on the oxide layer 208, the glass layer 212 on the surface of the polysilicon field plate 210, the silicon nitride layer 214 on the glass layer 212, and the Metal field plate 216 on glass layer 212 and below silicon nitride layer 214 . One of the voltage divider rings 206, and the oxide layer 208, polysilicon field plate 210, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com