Lead frame structure and surface sticking semiconductor packaging structure formed by same

A surface-attached, packaged structure technology, applied in semiconductor devices, semiconductor/solid-state device components, electrical solid-state devices, etc., can solve the problems of power reduction, bonding strength reduction, affecting the performance of the transient voltage suppression chip 11, etc. Improve the reliability of components and protect the chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

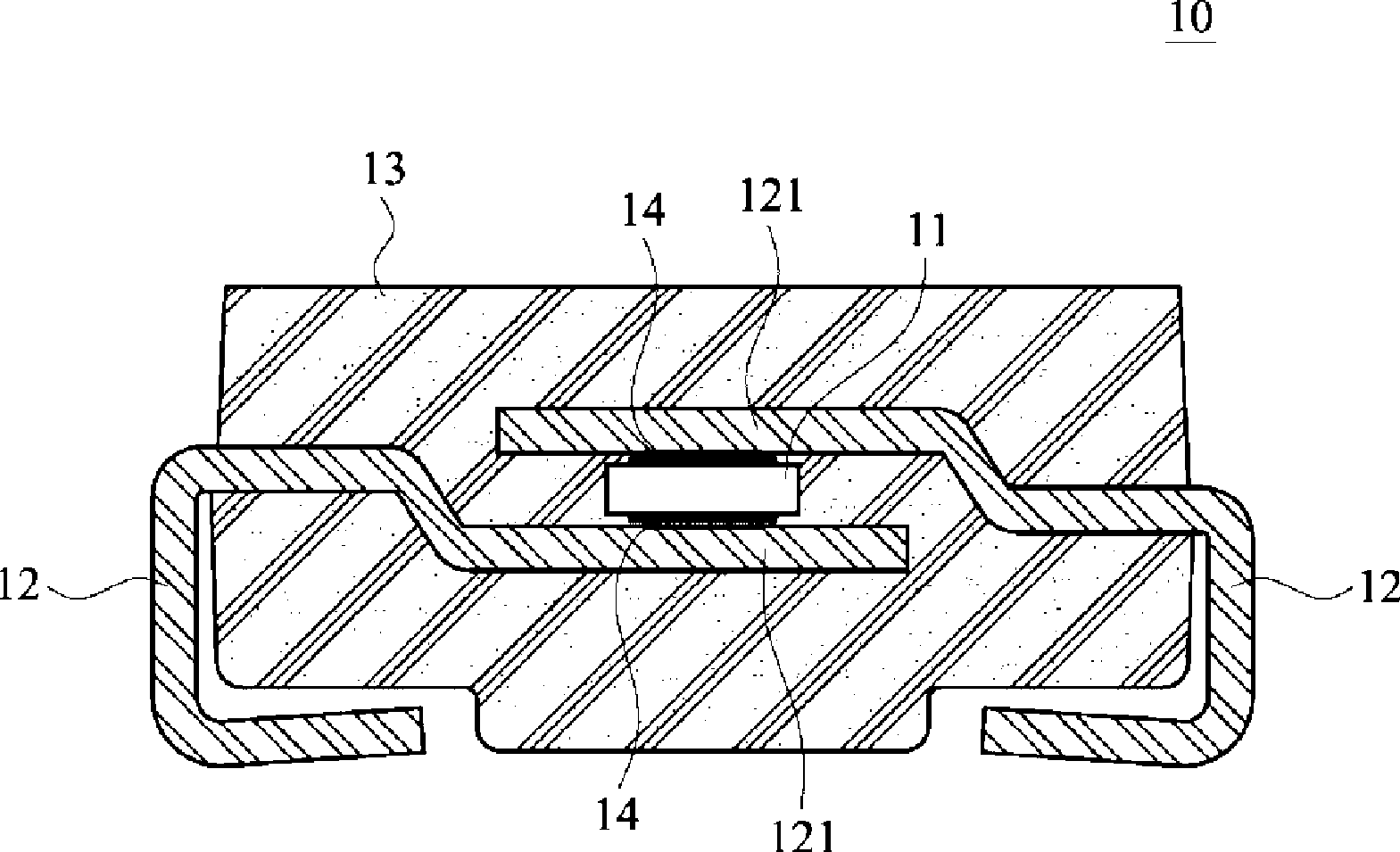

[0052] Figure 4 It is a cross-sectional view of a surface mount semiconductor package structure according to an embodiment of the present invention.

[0053] Such as Figure 4 As shown: the surface mount type semiconductor package structure 20 includes: a chip 30 , two lead frames 40 and a package body 50 .

[0054] Figure 5 It is a partial cross-sectional view of a surface-mount semiconductor package structure according to an embodiment of the present invention.

[0055] Chip 30 may be a transient voltage suppression chip. Such as Figure 5 As shown: the chip 30 includes a first surface 31 and a second surface 32, and the first surface 31 and the second surface 32 are respectively provided with square soldering surfaces 311, 321. The chip 30 can be welded to the lead frame 40 by using the solder 14, and the area of the square soldering surfaces 311, 321 is smaller than the area of the first surface 31 and the second surface 32, which can avoid the possibility that ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com