Method for determining shortest route of network on RDT sheet

An on-chip network and routing technology, applied in the computer field, can solve problems such as inability to produce global optimization results, reduced time complexity, and low performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0068] Below in conjunction with accompanying drawing and implementation method, the present invention is described in further detail:

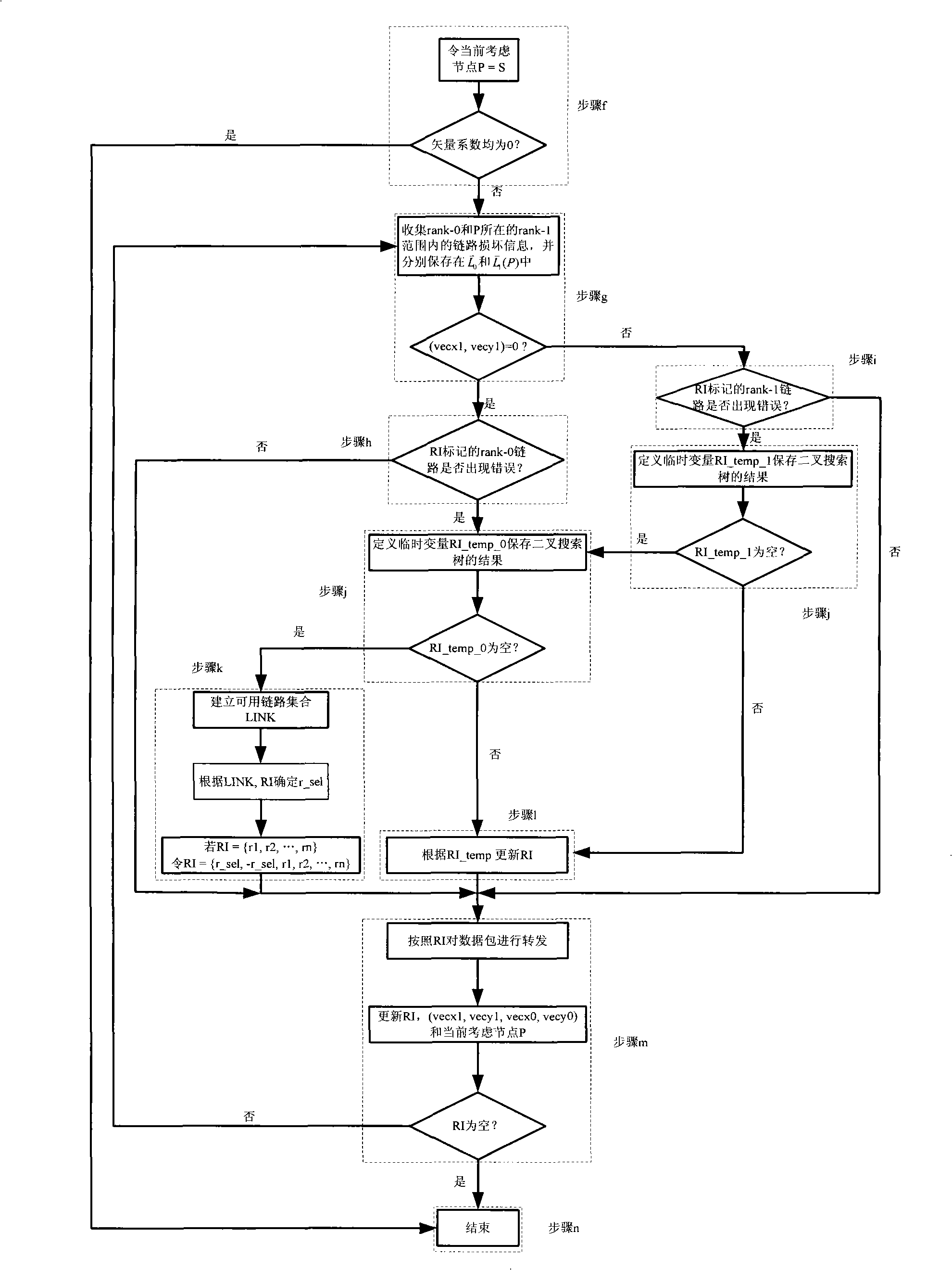

[0069] figure 1 It is a flow chart of the method for determining the shortest route with global optimization fault-tolerant capability for RDT (n, 1) on-chip network proposed by the present invention. The figure includes a total of seven processes: corresponding to the seven steps introduced before, and the flow chart of the fault-tolerant processing mechanism in step (7) is in figure 2 are described in detail. figure 2 The dotted boxes in represent the sub-steps in the fault-tolerant processing mechanism. The following takes the 16×16 RDT (2, 1) on-chip network as an example to explain one by one figure 1 The implementation of each process is shown.

[0070] Step (1) Establish a coordinate system for the RDT rank-0 network, determine the node number and the position of the communication node:

[0071] First determine the size of the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com