Multi-core onboard spacecraft computer based on FPGA

A spaceborne computer, multi-core technology, applied in the field of aerospace data processing, can solve the problem of slow processing speed of spaceborne computer, achieve the effect of retaining flexibility, improving performance, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

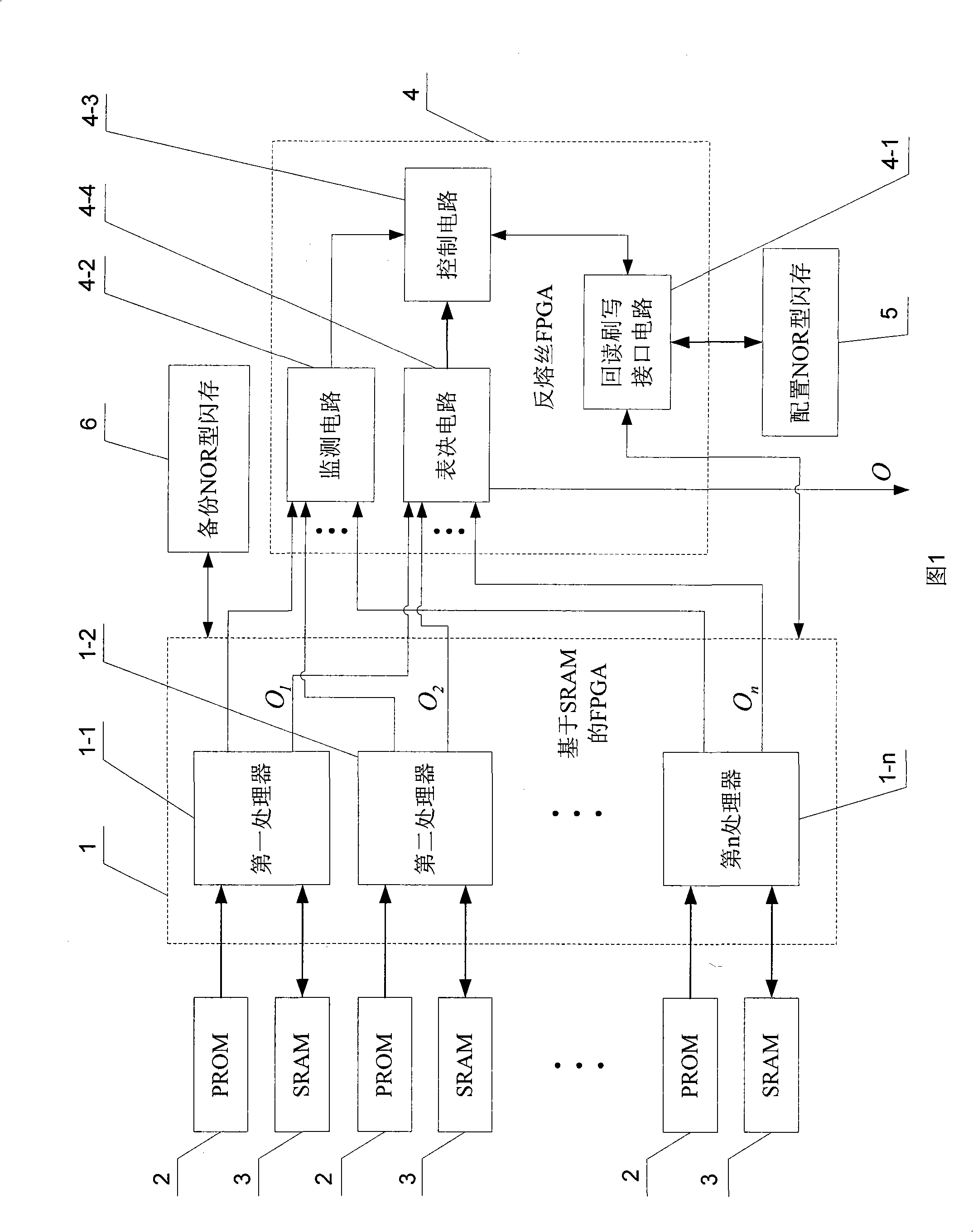

[0007] Specific embodiment one: below in conjunction with Fig. 1 illustrate present embodiment, present embodiment comprises FPGA1 based on SRAM, n PROM2, n SRAM3, antifuse FPGA4 and configuration NOR type flash memory 5,

[0008] The FPGA1 based on SRAM comprises n processors, which are respectively the first processor 1-1, the second processor 1-2 ... the nth processor 1-n, and the input end of each processor is connected to the input terminal of a PROM2. The output terminals are connected, and the cache input and output terminals of each processor are connected to the input and output terminals of a SRAM3.

[0009] The antifuse FPGA4 includes a read-back brush interface circuit 4-1, a monitoring circuit 4-2 and a control circuit 4-3, and the configuration file input and output terminals of the read-back brush interface circuit 4-1 and the configuration file of FPGA1 based on SRAM The input and output terminals are connected, the heartbeat signal output terminal of the first...

specific Embodiment approach 2

[0016] Embodiment 2: The difference between this embodiment and Embodiment 1 is that the heartbeat signal is a pulse signal output by the I / O port of the processor, and other components and connection methods are the same as Embodiment 1.

[0017] The normal output pulse signal is a waveform with high and low level changes according to a certain period, similar to a heartbeat signal; abnormality means that the output pulse signal is always high, often low or has an irregular cycle.

specific Embodiment approach 3

[0018] Specific embodiment three: the difference between this embodiment and embodiment one is that it also includes a backup NOR flash memory 6, the input and output terminals of the backup NOR flash memory 6 are connected with the data input and output terminals of FPGA1 based on SRAM, and other components And the connection method is the same as the first embodiment.

[0019] Since the SRAM-based FPGA1 has power-off data volatility, it brings the problem of information loss to the on-board computer system. In order to solve this problem, the SRAM-based FPGA1 needs to be reconfigured before it is reconfigured with new functional modules. Through a certain memory access instruction, the data to be protected in the SRAM-based FPGA1 is read into the backup NOR flash memory 6, and when the SRAM-based FPGA1 is powered on again, the SRAM-based FPGA1 is read back from the backup NOR flash memory 6 The data is protected, which greatly improves the security of the on-board computer s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com