Nonvolatile semiconductor memory

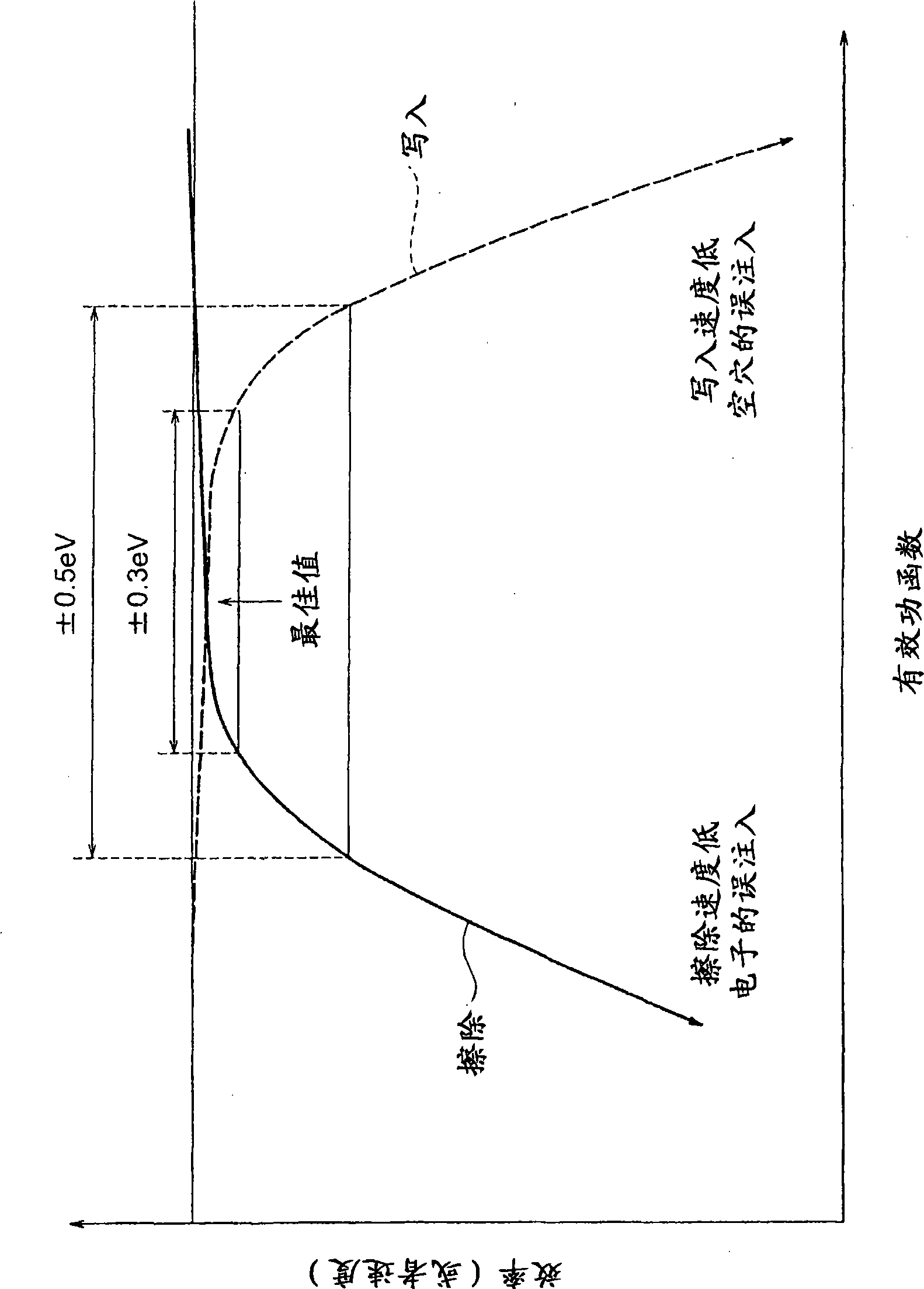

一种非易失性、半导体的技术,应用在半导体器件、半导体/固态器件制造、电固体器件等方向,能够解决有效功函数控制困难等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

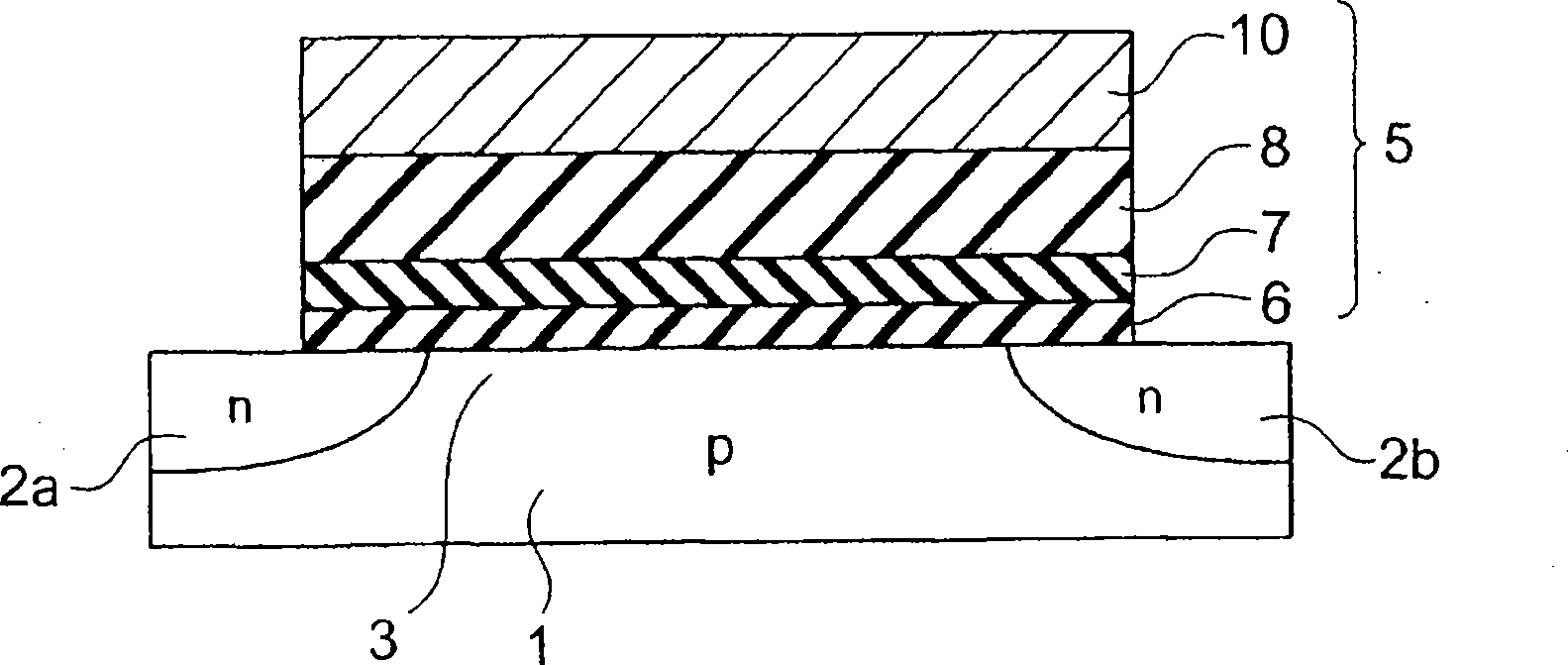

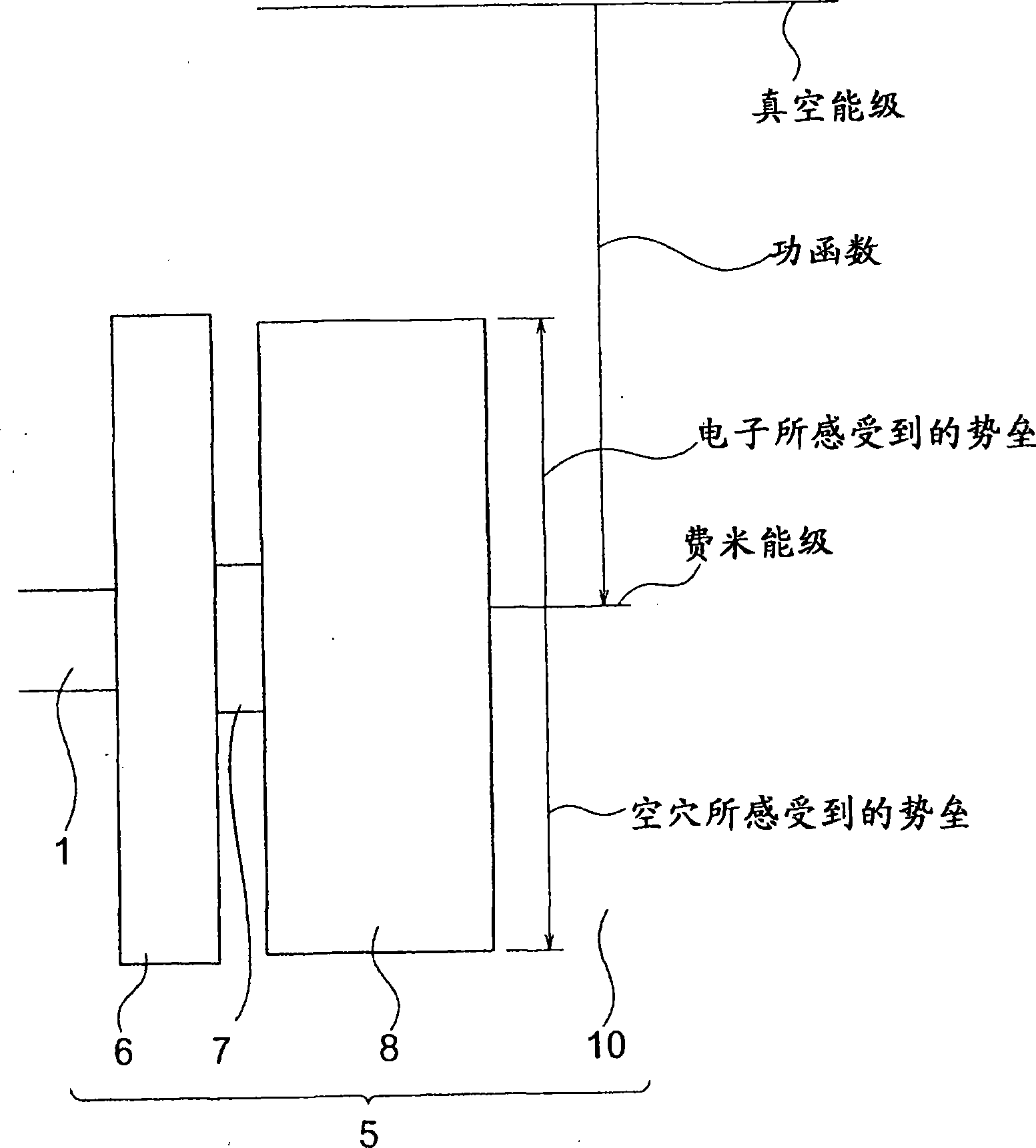

[0077] Next, refer to figure 1 A nonvolatile semiconductor memory according to a first embodiment of the present invention will be described. The nonvolatile semiconductor memory of this embodiment has a plurality of memory cells arranged in a matrix. figure 1 A cross section of each memory cell is shown. In each storage unit, such as figure 1 As shown, an n-type source region 2 a and an n-type drain region 2 b are separately formed in a p-type silicon substrate 1 . The region of the silicon substrate between the source region 2a and the drain region 2b becomes the channel region 3 as a current path. On the channel region 3, a gate 5 for controlling the operation of the memory is provided. The gate 5 has a stacked structure in which a tunnel insulating film 6 , a charge accumulation film 7 , a charge blocking film 8 , and a control electrode 10 are sequentially stacked on the channel region 3 . figure 2 The energy band structure of this gate 5 is shown.

[0078] Next, e...

no. 2 example

[0099] Next, refer to Figure 14 A nonvolatile semiconductor memory according to a second embodiment of the present invention will be described. The nonvolatile semiconductor memory of this embodiment has a plurality of memory cells arranged in a matrix. Figure 14 A cross section of each memory cell is shown. In addition to the control electrode, the memory cell of this embodiment has the same figure 1 The memory cells of the first embodiment shown have exactly the same structure. That is, the storage unit of this embodiment, such as Figure 14 As shown, an n-type source region 2 a and an n-type drain region 2 b are separately formed in a p-type silicon substrate 1 . The region of the silicon substrate between the source region 2a and the drain region 2b becomes the channel region 3 as a current path. On the channel region 3, a gate 5C for controlling the operation of the memory is provided. Gate 5C has a stacked structure in which tunnel insulating film 6 , charge accu...

no. 3 example

[0114] Next, refer to Figure 17 A nonvolatile semiconductor memory according to a third embodiment of the present invention will be described. The nonvolatile semiconductor memory of this embodiment has a plurality of memory cells arranged in a matrix. Figure 17 A cross section of each memory cell is shown. In addition to the control electrode, the memory cell of this embodiment has the same figure 1 The memory cells of the first embodiment shown have exactly the same structure. That is, in the storage unit of this embodiment, as Figure 17 As shown, an n-type source region 2 a and an n-type drain region 2 b are separately formed in a p-type silicon substrate 1 . The region of the silicon substrate between the source region 2a and the drain region 2b becomes the channel region 3 as a current path. On the channel region 3, a gate 5F for controlling the operation of the memory is provided. The gate 5F has a stacked structure in which a tunnel insulating film 6 , a charge...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com