Method for manufacturing mask ROM

A manufacturing method and mask read-only technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of reducing the resistance value of gate structure, memory performance interference, large resistance value of active area of peripheral logic circuits, etc. problems, to avoid mixing, reduce process complexity, and avoid interfering with memory performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the technical features of the present invention more comprehensible, the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

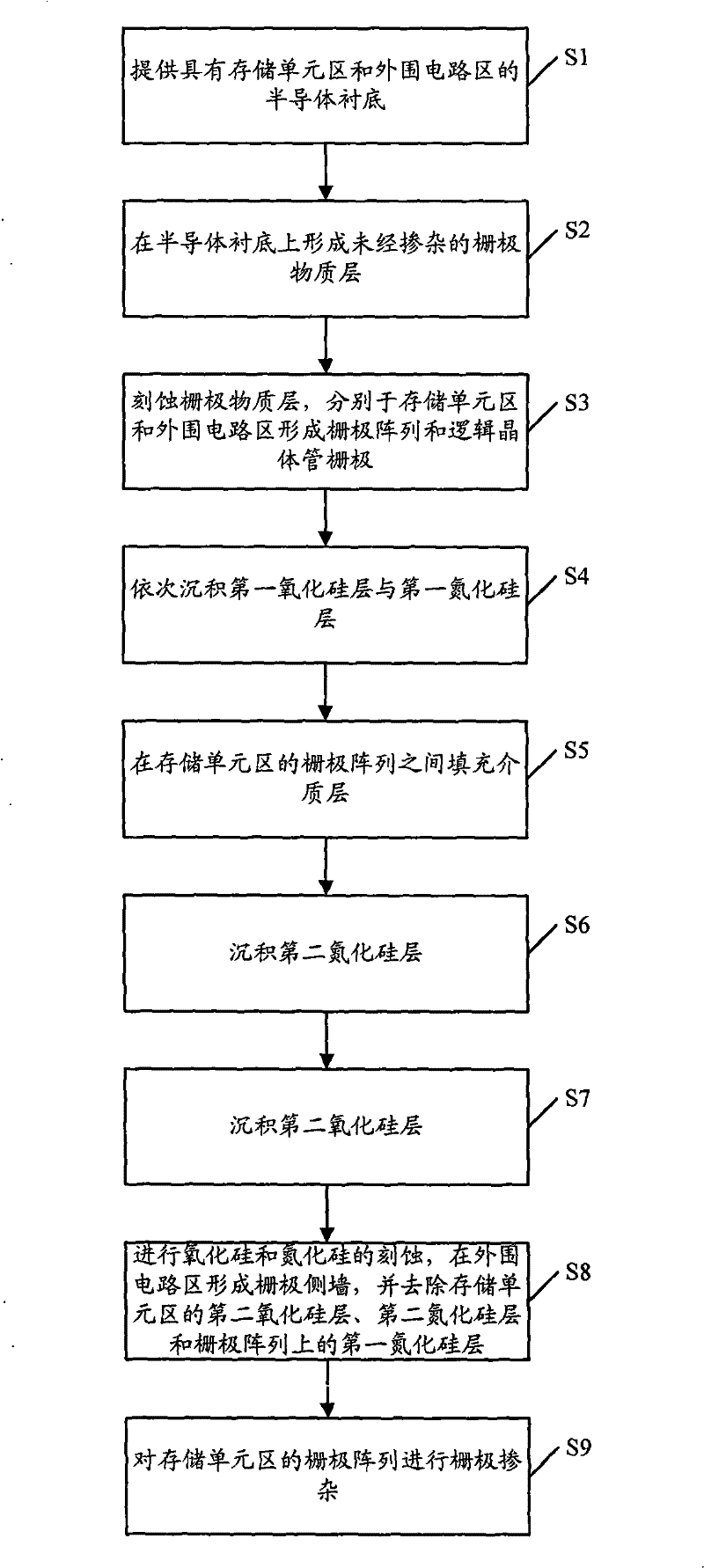

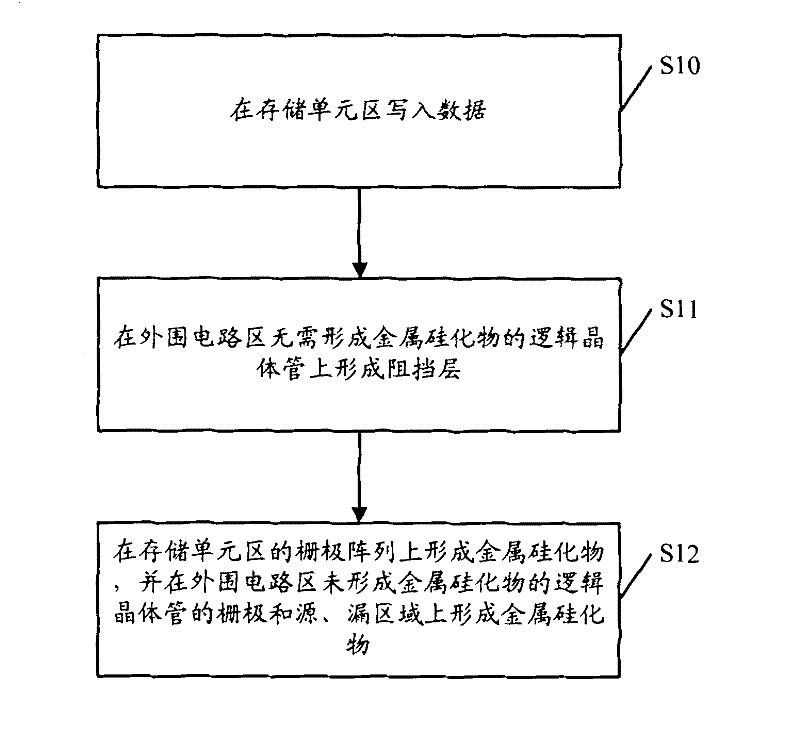

[0027] Please refer to figure 1 , which is a schematic flow chart of a mask ROM manufacturing method provided by an embodiment of the present invention. As shown in the figure, the manufacturing method of the mask ROM includes the following steps:

[0028] S1: providing a semiconductor substrate having a memory cell region and a peripheral circuit region;

[0029] S2: forming an undoped gate material layer on the semiconductor substrate;

[0030] S3: Etching the gate material layer to form a gate array and a logic transistor gate in the memory cell area and the peripheral circuit area respectively;

[0031] S4: sequentially depositing a first silicon oxide layer and a first silicon nitride layer;

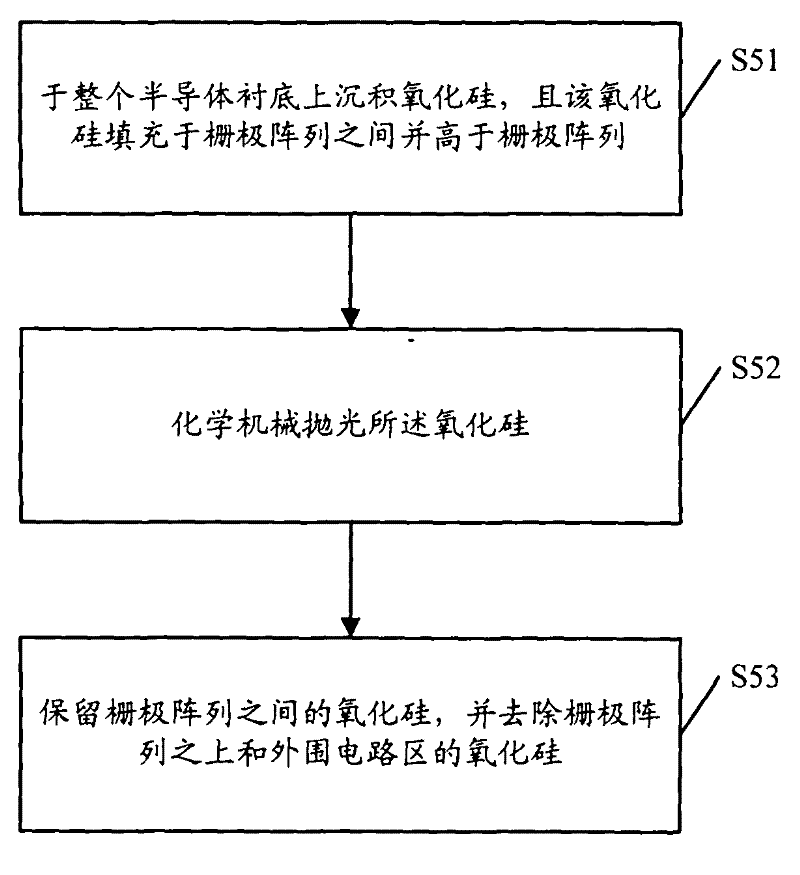

[0032] S5: filling a dielectric layer (usually a silicon oxide laye...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com