Chip bearing belt and chip packaging construction

A technology of chip packaging structure and carrying tape, which is applied in the direction of electrical components, electric solid devices, circuits, etc., and can solve problems that affect the reliability of the overall components, alignment difficulties, and chips that cannot be installed correctly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

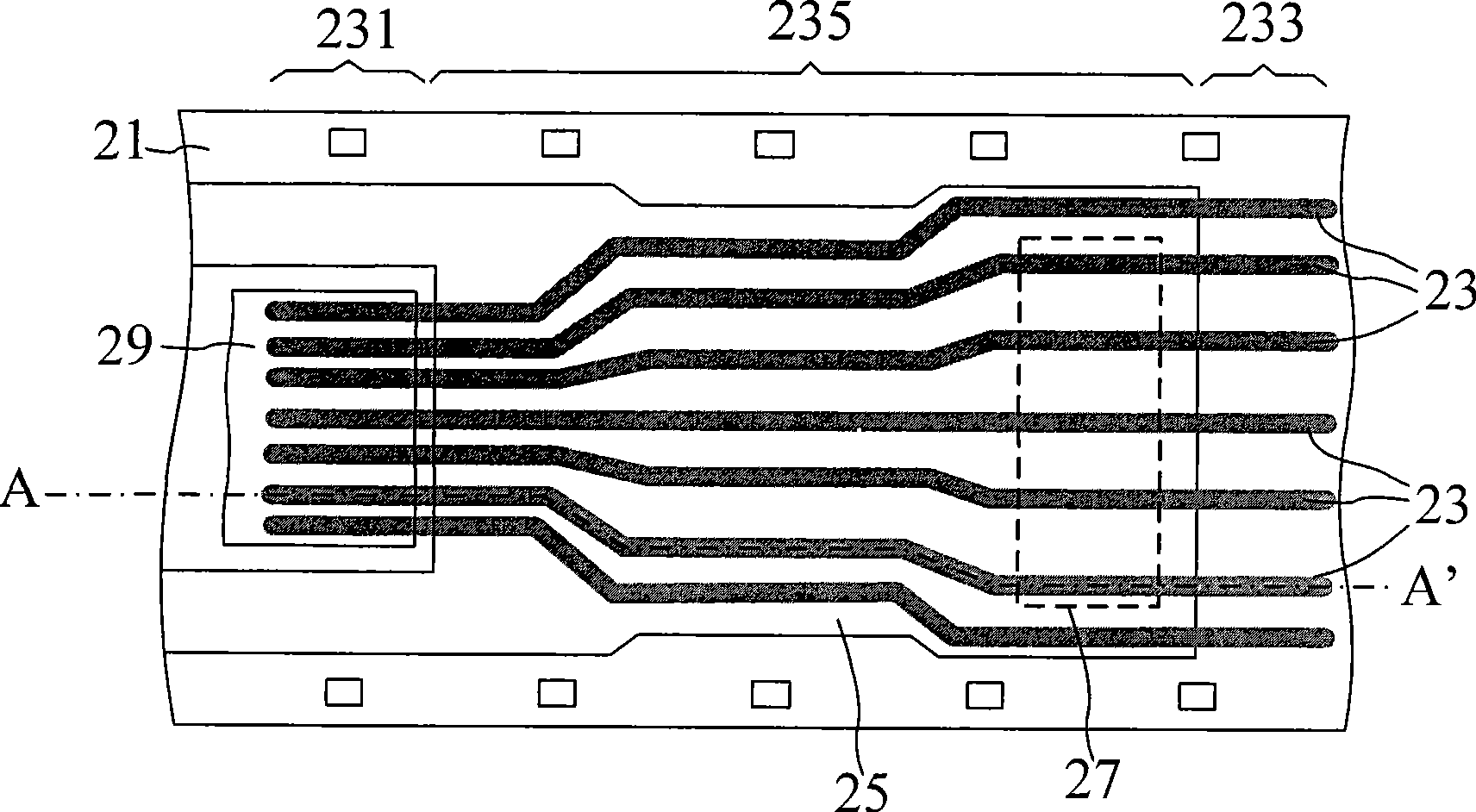

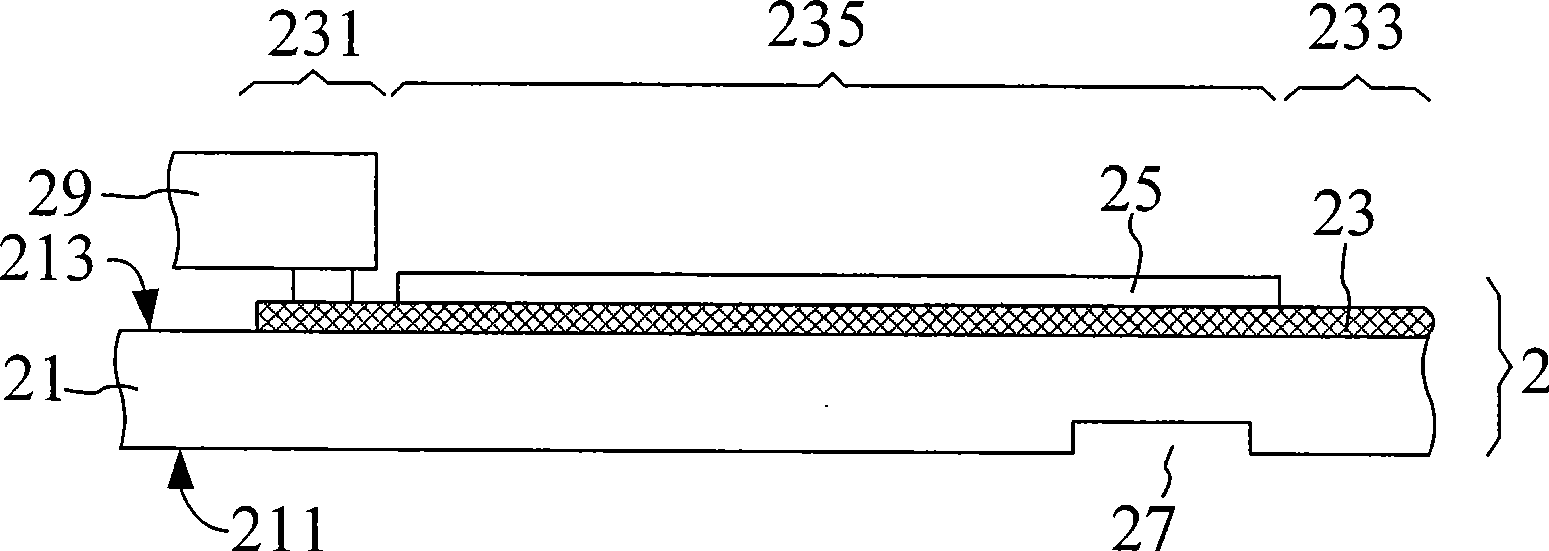

[0030] Also refer to Figure 2A and 2B ,in Figure 2A It is a schematic top view of the chip carrier tape 2 of the present invention, and Figure 2B for Figure 2A Sectional view at section line AA' in middle. The chip carrier tape 2 of the present invention includes a flexible substrate 21 , a patterned conductive layer 23 , and a solder resist layer 25 . The flexible substrate 21 is a polymer substrate, usually polyimide (PI) substrate. The flexible substrate 21 has a first surface 211 and a second surface 213 opposite to the first surface 211 . Wherein, a first recessed structure 27 is disposed on the first surface 211 . When the chip carrier tape 2 enters a low-temperature environment from a high-temperature environment (for example, after baking), because the flexible substrate 21 and the patterned conductive layer 23 have different thermal expansion coefficients (for example, the thermal shrinkage of metal copper is greater than that of polyamide imine), will lead...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com