Large capacity image data real-time compressing apparatus and method based on multi-DSP parallel processing

A technology of image data and parallel processing, applied in the field of information processing, can solve the problem of large difference in processor cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

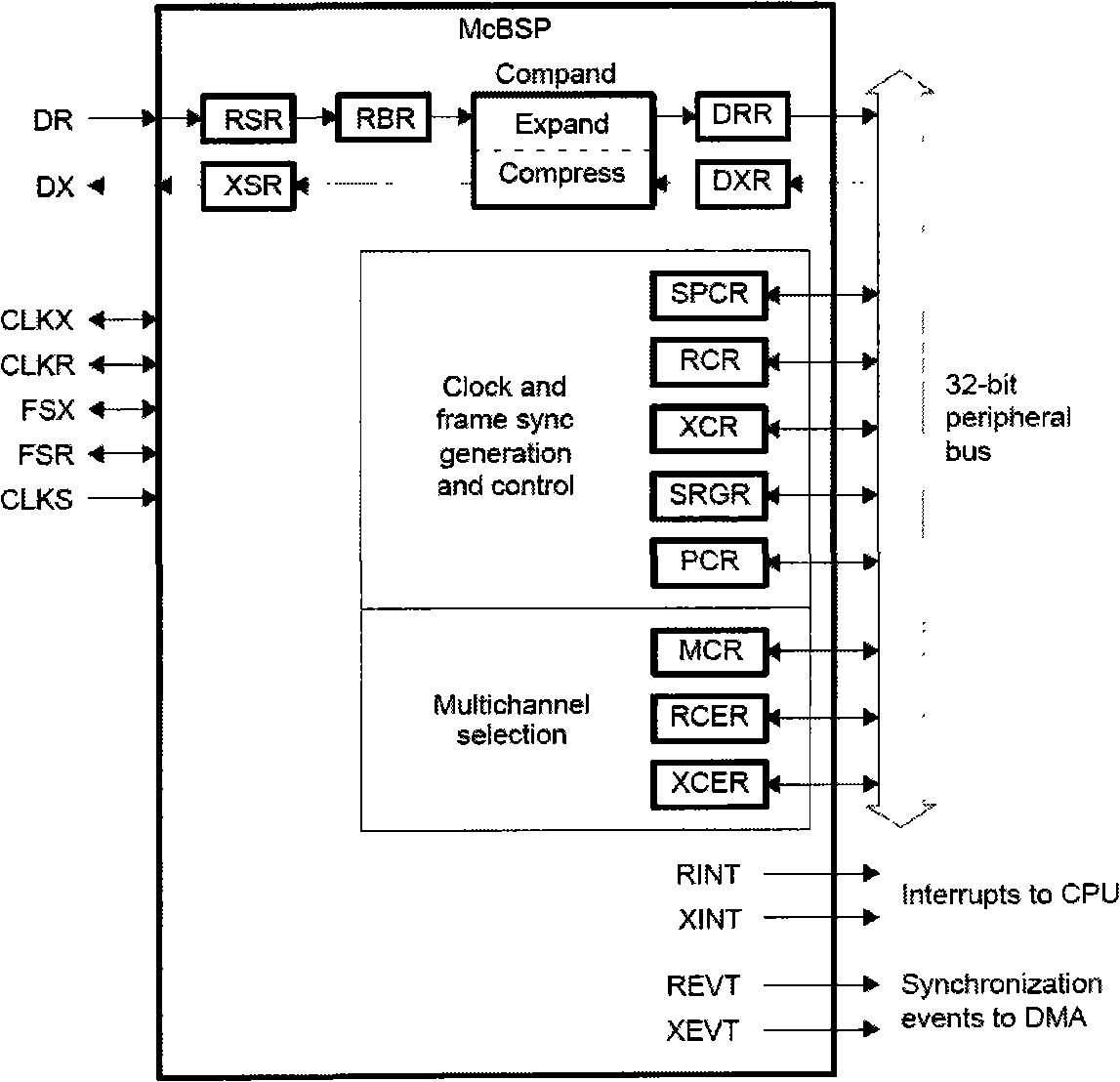

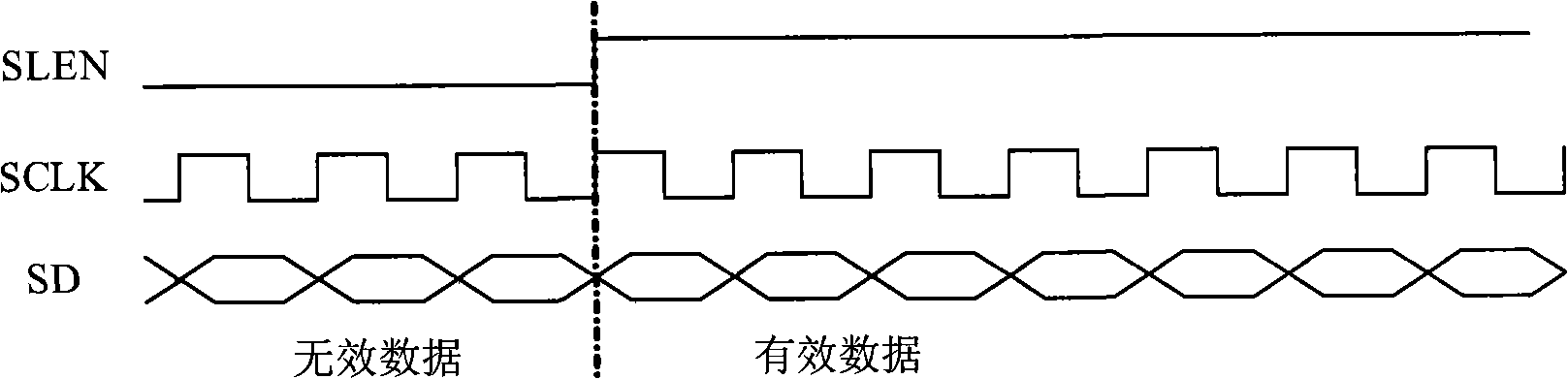

[0035] Such as figure 1 Shown in is a block diagram of the overall structure of a large-capacity image data real-time compression device based on a multi-DSP parallel processing structure. The n-channel serial CCD data enters the FPGA in parallel through the LVDS (Low Voltage Differential Signaling) interface for timing conversion, and multiple parallel DSPs use EDMA (Extend Direct Memory Access) through two serial ports. Read two channels of camera data from FPGA and cache, compress and encode. The entire data compression system requires (int)((n+1) / 2) DSPs to process in parallel. The compressed code stream data is output to the FPGA through the serial port, and the FPGA re-buffers, frames, and outputs after timing conversion. The control device FPGA of the present invention completes the management of the data flow and the management of each DSP, and the image data output by the camera enters each DSP of the data compressor in parallel, and the FPGA basically does not proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com