Self-aligning shallow groove isolation structure, memory unit and method for forming the same

A technology of memory cells and isolation structures, applied in electrical components, electrical solid-state devices, semiconductor devices, etc., can solve problems such as leakage current and affecting device reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

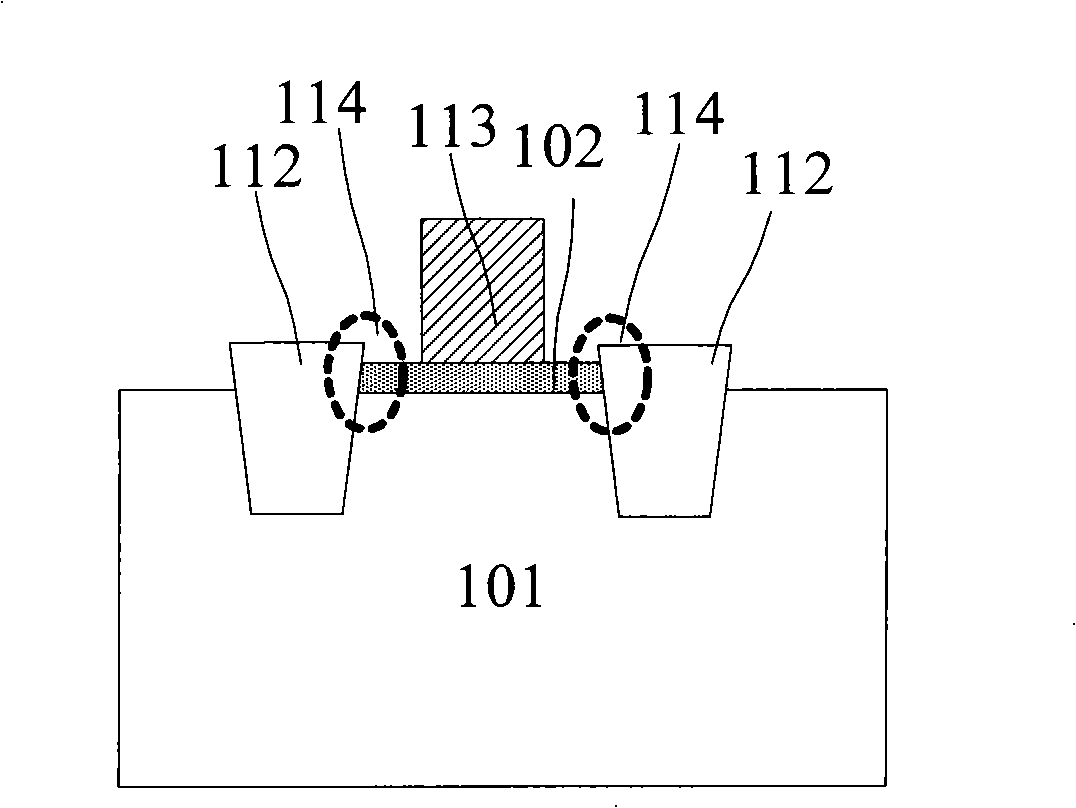

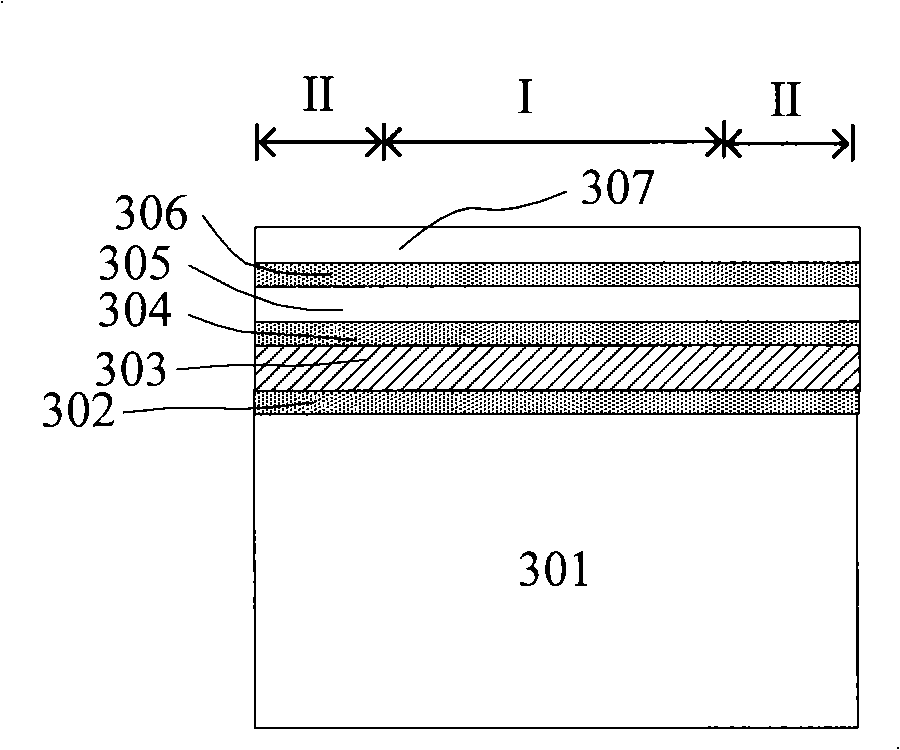

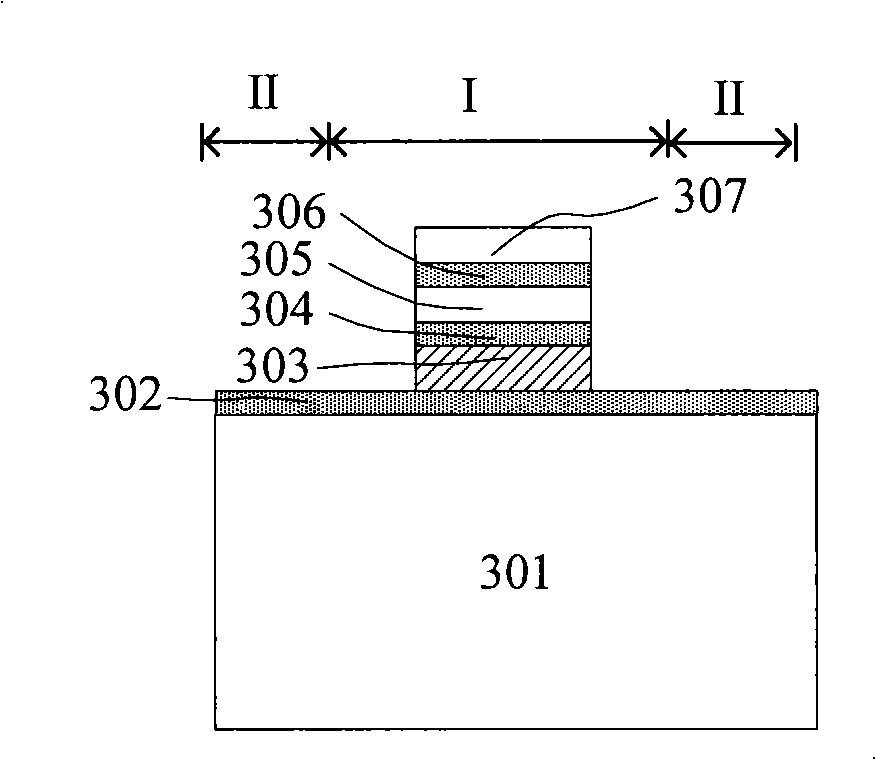

[0025] The essence of the present invention is to provide a method for forming a self-aligned shallow trench isolation structure. In the present invention, an oxidation step is added to the process of adopting a self-aligned shallow trench isolation structure, at the junction of the active region and the isolation region, A field oxide layer is formed by oxidation at the junction of the gate dielectric layer and the semiconductor substrate, which prevents the formation of sharp corners at the contact between the self-aligned shallow trench isolation structure and the gate dielectric layer, thereby preventing leakage current caused by the existence of the sharp corners. In the embodiment of the present invention, the semiconductor substrate is p-type, and the formed MOS transistor is an n-type channel. The semiconductor substrate can also be n-type, and the MOS transistor can also be a p-type channel, which should not be too limited here. protection scope of the present inventio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com