Scanning chain diagnosis vector generation method and device and scanning chain diagnosis method

A technology for generating a device and a diagnosis method, which is applied in the field of scan chain diagnosis and can solve problems such as misdiagnosis of combinational logic

Active Publication Date: 2008-10-15

INST OF COMPUTING TECH CHINESE ACAD OF SCI

View PDF0 Cites 13 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

The present invention aims at the deficiencies in the prior art that may lead to misdiagnosis due to faults in combinatorial logic when performing scan chain diagnosis, thereby proposing a scan chain diagnostic vector generation method and device capable of tolerating combinatorial logic faults and a scan chain diagnostic method

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

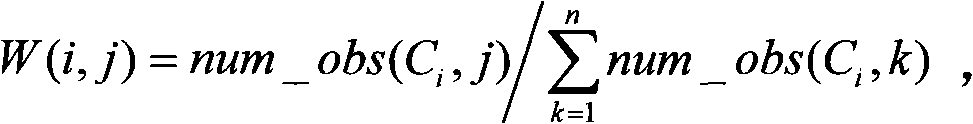

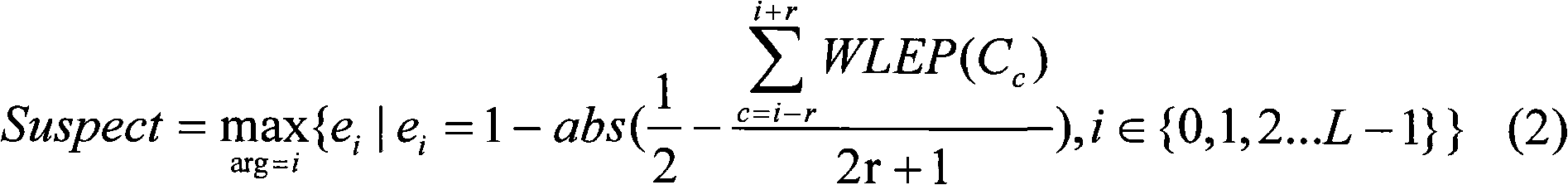

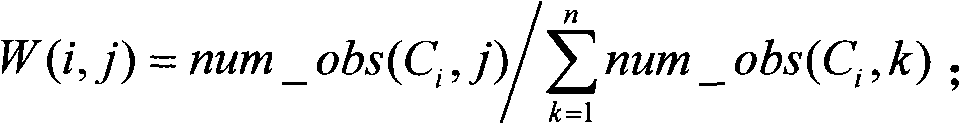

The invention provides a method and a device for generating scanning chain diagnostic vector and a diagnostic method of a scanning chain. The method for generating diagnostic vector comprises the following steps that: the failure type of a scanning chain is determined; a constraint condition is set according to the failure type of the scanning chain; under the constraint condition, the logic state of a scanning unit can obtain maximum transmitted output or false output number through a path formed by combinational logic, thereby generating scanning chain diagnostic vector. The device for generating diagnostic vector comprises the following parts: a failure type distinguishing unit used to judge the failure type of a scanning chain, a constraint condition unit used to set a constraint condition according to a failure type and a diagnostic vector generating unit used to ensure that the logic state of a scanning unit can obtain maximum transmitted output or false output number through a path formed by combinational logic so as to generate scanning chain diagnostic vector. The method and the device can effectively tolerate the failure in combinational logic without bringing hardware spending to a circuit.

Description

Method and device for generating scan chain diagnostic vector and scan chain diagnostic method technical field The invention relates to a fault location method for a logic integrated circuit, in particular to a diagnostic vector generation method and device for a scan chain fault in a logic integrated circuit and a scan chain diagnosis method. Background technique Scan technology is a widely used structured design for testability (DesignForTestability, DFT) technology. Scan-based logic diagnostics have become an indispensable means of yield ramp-up. Logical diagnosis can help failure analysis equipment quickly find the defect location that causes failure, thereby accelerating the failure analysis process. The scan technology is to insert a shift register structure called a scan chain into the logic integrated circuit. Through the scan chain, the effective transmission of test data and the effective export of the internal state of the chip can be realized very convenientl...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G01R31/3185

Inventor 王飞胡瑜李晓维

Owner INST OF COMPUTING TECH CHINESE ACAD OF SCI

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Patsnap Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com